# **Qucs-S Help Documentation**

Release 0.0.19-S

Contributing Authors 2015, 2016

Oct 07, 2017

# Contents

1 User Manual and Reference Material

# CHAPTER 1

#### User Manual and Reference Material

Authors Mike Brinson (mbrin72043@yahoo.co.uk) and Vadim Kusnetsov (ra3xdh@gmail.com)

Copyright 2015, 2016

Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.1 or any later version published by the Free Software Foundation. A copy of the license is included in the section entitled "GNU Free Documentation License".

Contents:

### **Chapter 1. Introduction**

Following the release of Qucs-0.0.18 in August 2014 the Qucs Development Team considered in detail a number of possible directions that future versions of the software could take. Spice4qucs is one of these routes. It addresses a number of problems observed with the current version of Qucs while attempting to combine some of the best features of other GPL circuit simulation packages. The project also aims to add additional model development tools to those currently available in Qucs-0.0.18. Qucs was originally written as an RF and microwave engineering design tool which provided features not found in SPICE, like S parameter simulation, two and multiport small signal AC circuit analysis and RF network synthesis. Since it was first release under the General Public License (GPL) in 2003 Qucs has provided users with a relatively stable, flexible and reasonably functional circuit simulation package which is particularly suited to high frequency circuit simulation. In the years following 2003 the Qucs Development team added a number of additional simulation facilities, including for example, transient simulation, device parameter sweep capabilities and single tone Harmonic Balance simulation, making Qucs functionality comparable to SPICE at low frequencies and significantly extended at high frequencies. Considerable effort has also been made to improve the

device modelling tools distributed with Ques. The recent versions of the software include code for algebraic equation manipulation, Equation-Defined Device (EDD) modelling, Radio Frequency Equation-Defined Device (RFEDD) simulation and Verilog-A synthesised model development plus a range of compact and behavioural device modelling and post simulation data analysis tools that have become central features in an open source software package of surprising power and utility.

One of the most often requested new Ques features is "better documentation", especially documentation outlining the use and limitations of the simulation and the modelling features built into Ques. Ques is a large and complex package which is very flexible in the way that it can be used as a circuit design aid. Hence, however much documentation is written describing its functionality there are always likely be simulation and modelling examples that are missing from the Ques documentation. In future Ques releases will be accompanied by two or more basic Ques documents. The first of these, simply called "Ques-Help", provides introductory information for beginners and indeed any other users, who require help in starting to use Qucs. The second Qucs document, called "Spice4qucs-Help", introduces more advanced simulation and modelling topics. Both documents present a large number of typical circuit simulation and compact device modelling examples. In the text these are also linked to sets of Ques reference material. Since 2003 the Ques Development Team, and other authors, have published a body of work concerning Ques and its applications. A bibliography of these publications can be found at the end of this document. Anyone interested in learning about Ques is recommended to read these publications as they provide a wealth of information on basic and advanced Ques topics. Both the "Ques Help" and "Spice4ques-Help" documents are very much work in progress. Updated versions will be published with each new Ques release. Moreover, to keep everyone up to date with Ques current developments it is planned to updated them during future Ques development phases. The latest documentation can be found at https://github.com/Qucs/qucs-help.

#### 1.1 Background

The current rate of Qucs downloads from http://qucs.sourceforge.net/ is around 3000 per week with a total of roughly 1.5 million downloads since Qucs was first released in 2003. This figure does not however, imply that 1.5 million copies of Qucs are currently in regular use. It does perhaps give an indication of the popularity of the software, particularly amongst users interested in RF circuit design and simulation. For a high percentage of regular Qucs users the current distribution version (Qucs 0.0.18) provides a reasonably stable and accurate simulation tool equipped with more than enough facilities to meet their everyday needs. In reality Qucs is not perfect but includes a number of weaknesses and known limitations. The onward march of technology also makes it imperative that Qucs evolves from a traditional circuit simulator to a design tool that can handle modelling and simulation of circuits which include devices from new emerging technologies. Today Qucs includes an extensive range of component, device and circuit modelling tools, allowing it to model and simulate circuits built from standard components and new production devices.

Three of the primary aims of the work undertaken by the Qucs Development Team are firstly to remove software bugs and improve the overall performance of the package, secondly to address known weaknesses and limitations and thirdly to develop the package by adding features which increase it's utility. Readers who are not familiar with open source software development may be unaware of how the development process works. By "Qucs Development Team" we mean a group of interested individuals who freely give both their time and expertise for the improvement of the GPL Qucs package. The Qucs Development Team is not a fixed group but is a dynamic organisation where different people contribute, simultaneously or at different times, to the same part or different parts of the software. The spice4qucs project group is one of a number of sub-groups within the overall Qucs Development Team. It was formed to address the known limitations of the previous Qucs releases and to take advantage of the work done by other GPL circuit simulation teams working on the Ngspice ( http://ngspice.sourceforge.net/ ), Xyce ( https://xyce.sandia.gov/ ) and SPICE OPUS (http://www.spiceopus.si/) circuit simulators.

The spice4qucs initiative is an ongoing project which attempts to:

Correct known weaknesses observed with the current Qucs analogue simulation engine "qucsator". Qucsator is based on classical numerical mathematics routines for the solution of electrical network linear and non-linear real and complex algebraic equations and time domain algebraic and differential equations. For small circuits, qucsator works well in the DC and AC small signal domains. However, in the transient and Harmonic Balance simulation domains it can fail to converge to an acceptable solution. Its performance is also often below that expected of a modern circuit simulator employing sparse matrix algorithms. However, quesator works well for RF small signal AC simulation and will for some time remain the first choice for this simulation domain.

- 2. Provide Qucs users with a choice of simulation engine selected from qucsator, Ngspice, Xyce and SPICE OPUS. By selecting Ngspice, Xyce or SPICE OPUS as the Qucs simulation engine users may capitalise on all the features offered by the extensive SPICE developments which have taken place over the last forty years. Both Ngspice, Xyce and SPICE OPUS offer improved transient simulation convergence and speed, particularly for large non-linear circuits. Xyce brings an alternative implementation of single tone Harmonic Balance simulation to Qucs which offers much improved convergence properties for both linear and non linear components and devices. The latest version of Xyce, 6.5 at the time of writing, also offers multi-tone Harmonic Balance simulation. SPICE OPUS adds transient shooting methods for the steady state analysis of large signal AC simulation and optimization.

- 3. Extend Ques subcircuit, Equation-Defined Device (EDD), Radio Frequency Equation-Defined Device (RFEDD) and Verilog-A device modelling capabilities. The latest spice4ques release (Ques-0.0.19-S) offers much improved component and device modelling features that work as interlinked tools, supporting model development as a continuous flow from physical concept to compiled C/C++ code. This feature is centred around a "turn-key" version of the XSPICE Code Model construction tools. If required the spice4ques project can also use the Berkeley "Model and Algorithm Prototyping Platform" (MAPP http://draco.eecs.berkeley.edu/ dracotiki/tiki-index.php?page=MAPP ) for compact model construction. It is also possible to synthesis Ngspice, Xyce SPICE OPUS SPICE netlists from Ques EDD and RFEDD models and to synthesise Verilog-A models from Ques EDD and SPICE B components.

- 4. Offer Ques users access to the additional simulation tools and extra component and device models provided by Ngspice, Xyce and SPICE OPUS. This includes much improved component library facilities which allow the use of device manufacturers SPICE models and XSPICE Code Models.

- 5. Offer for the first time with Qucs a true mixed-mode analogue-digital circuit simulation capability using Qucs/Ngspice/SPICE OPUS/XSPICE simulation.

The spice4qucs initiative is an on going project and must be considered as very much work in progress. In its early releases not all the features listed above will be available for public use. It is however, the intention of the Qucs Development Team to introduce them as quickly as possible. Other features not listed in the previous entries may also be introduced.

#### 1.2 Qucs-0.0.18 Structure

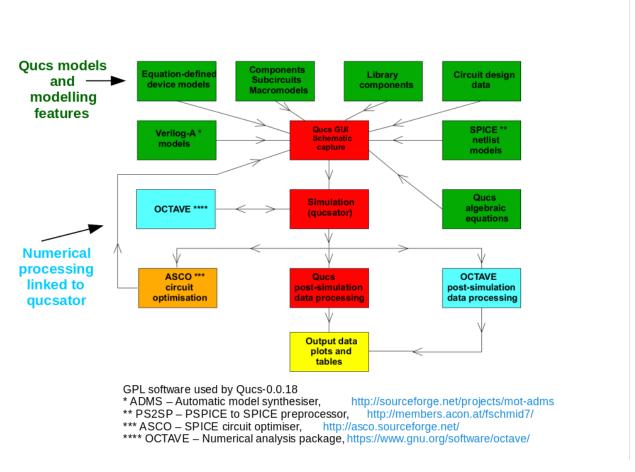

A block diagram showing the main analogue modelling and simulation functions of the Qucs-0.0.18 package is illustrated in Figure 1.1. For convenience, particularly easy identification, blocks with similar modelling or similar simulation functions have been coded with identical colours, for example dark red indicates the GUI and qucsator analogue simulation engine and dark green major component and device modelling tools. The direction of the flow of data between blocks are also shown with directed arrows. Central to the operation of the Qucs-0.0.18 package is the Qucs graphical user interface (GUI), the qucsator simulation engine and a post simulation data processing feature (indicated by the yellow block in Figure 1.1) for the extraction of device and circuit parameters and the visualisation of simulated signal waveforms. Cyan blocks in Figure 1.1 identify the well known Octave numerical analysis package ( https://www.gnu.org/software/octave/ ). Qucs employs Octave for additional post simulation data processing and waveform visualisation plus an experimental circuit simulation process where qucsator and Octave undertake cooperative transient circuit simulation (cyan coloured blocks). The single light brown block in Figure 1.1 represents the ASCO optimisation package which is used by Qucs for determining circuit component values and device parameters which result in specific circuit performance criteria.

Readers who are not familiar with the basic operation and use of the Ques GUI, circuit simulator and output processing routines should consult the "Ques-Help" document before proceeding further with this more advanced document.

Figure 1.1. A block diagram showing the analogue modelling and simulation facilities provided by Qucs-0.0.18.

#### 1.3 Qucs future capabilities

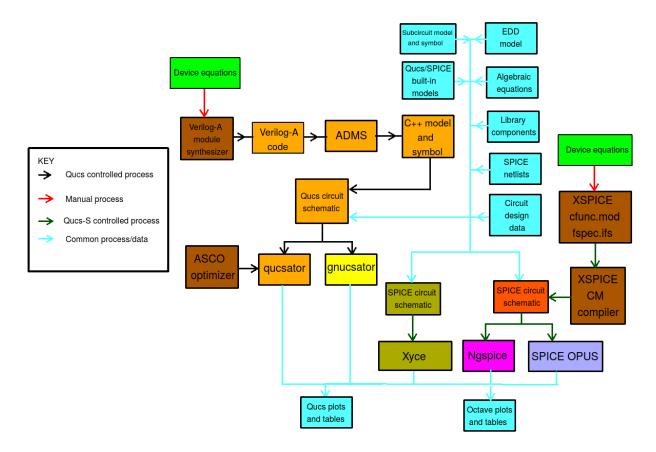

Figure 1.2. presents an extended version of the Qucs-0.0.18 functional diagram where the added blocks indicate areas chosen for current and future Qucs development. Two major extension to Qucs functionality are obvious, namely the addition of the Ngspice, Xyce and SPICE OPUS circuit simulators to the Qucs package and the increase in the Qucs device modelling capabilities through the addition of the XSPICE Code Modelling software. Figure 1.2. only gives a rough picture of the proposed changes to Qucs under development by the spice4qucs project. Much of the detail will become clearer later in the manual text and reference sections.

Figure 1.2. An block diagram outlining the extended Qucs-S simulation and modelling tools under development by the spice4qucs initiative.

#### 1.4 A first view of the extended spice4qucs device modelling and simulation features

At this point it seems appropriate to introduce a short example which demonstrates how much Qucs has evolved since the release of version 0.0.18. This example has been deliberately chosen to present an overview of the major new Qucs features either already developed by the spice4qucs project or planned for future releases. To provide readers with adequate information on how to make the best use of the new spice4qucs features they are described in detail in later chapters of this document.

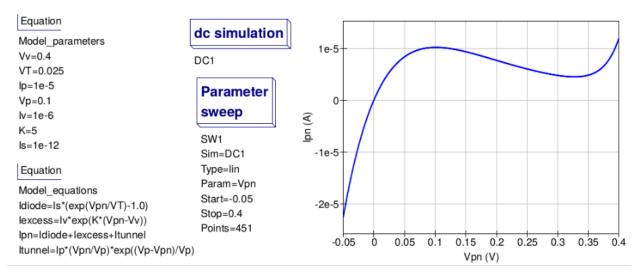

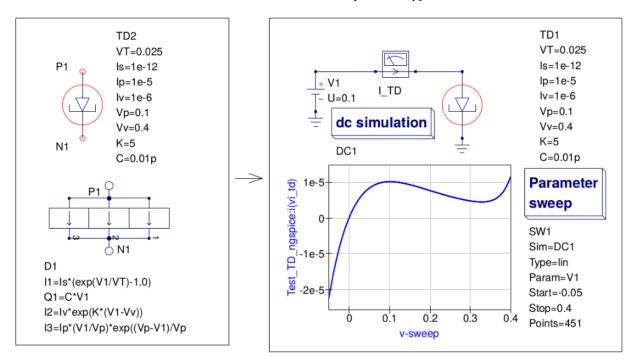

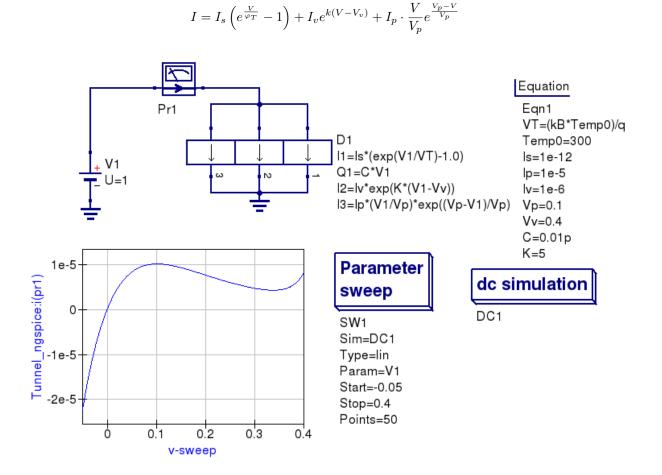

Ques version 0.0.18 is a surprisingly sophisticated program with quite a number of hidden features which are not obvious to most Ques users. Given in Figure 1.3 is a Ques schematic which demonstrates a little known application of the circuit simulator. Ques is ideal for developing high level behavioural models of new components or devices which are not implemented in the distributed software. The schematic in Figure 1.3. introduces the physical equations and device parameters for a semiconductor tunnel diode. By using the Ques parameter sweep and DC simulation operations it is possible to scan the diode bias voltage Vpn, calculate the tunnel diode bias current Ipn at each bias point and plot the device id = f(vd) characteristics. Note that in this introductory example the Ques schematic does not include any electrical components. Moreover, the tunnel diode current is calculated directly from its physical **model\_equations** and **model\_parameters**.

Figure 1.3. Mathematical representation of Id = f(Vd) for a semiconductor tunnel diode, including device model\_parameters, model\_equations and a Ques DC scan test.

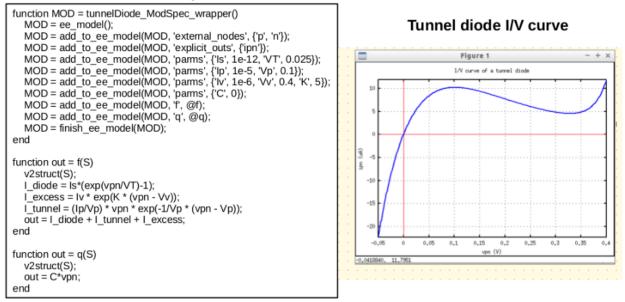

The Berkeley **Model and Algorithm Prototyping Platform** (MAPP) is a new GPL modelling and simulation tool. It is developed by the MAPP team at the Department of Elecrical Engineering and Computer Science, University of California, Berkeley using a MATLAB (copyright) subset common to the Octave numerical analysis software. As part of the spice4ques project the MAPP software has been interfaced with the Ques GUI. Figure 1.4 introduces a MAPP behavioural model for the tunnel diode in Figure 1.3. Notice how similar the models in Figures 1.3 and 1.4 are. MAPP circuit simulation results in the diode characteristic plotted in Figure 1.4.

#### MAPP tunnel diode compact device model

Figure 1.4. MAPP tunnel diode model and simulated diode current as a function of applied bias voltage.

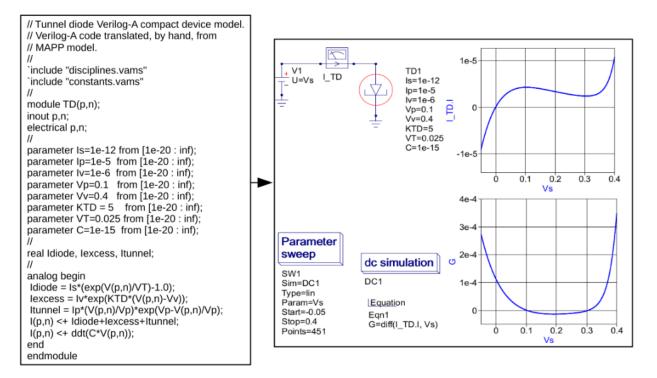

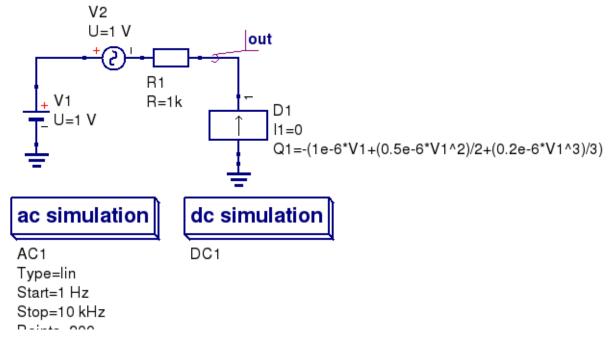

The Ques and MAPP modelling tools allow models represented by a set of mathematical equations based on the physical properties of a device to be tested and their correct operation confirmed prior to constructing a simulation model for inclusion in circuit schematics. Illustrated in Figure 1.5 is a third model for the tunnel diode plus a test circuit for simulating the device DC current versus voltage characteristics. This model will work with Ques-0.0.18 and spice4ques versions of the circuit simulator. It shows how a Ques EDD model represents the physical model of

the tunnel diode and how this model can be represented with it's own symbol and tested by combining it with other components to form a DC characteristic test circuit. The Ques EDD is not implemented in SPICE simulators. SPICE 3f5 and later simulators have instead other features like, for example, the B type sources.

Figure 1.5. Ques EDD behavioural model for the tunnel diode first introduced in Figure 1.3.

The Ques EDD component has one feature which makes it particularly important for developing compact device simulation models, namely that its structure and modelling capabilities are similar to those available with the Verilog-A hardware description language. Hence, once an MAPP/Ques EDD model is operating satisfactorily it can be transcribed into a Verilog-A compact model by inspection or by computer synthesis. Such a Verilog-A model and test circuit is shown in Figure 1.6.

Figure 1.6. A Verilog-A compact tunnel diode model and test circuit.

One of the main aims of the spice4qucs initiative is both to improve the Qucs compact device modelling capabilities and to streamline the flow of information between each part of the modelling and simulation sequence. In all Qucs releases prior to the spice4qucs project a number of modelling tools were implemented in the distribution software but users had to translate manually each type of model format to other formats if they wished to use a model with a different simulator or modelling tool. One exception was the rudimentary translation tool called **qucsconv** for translating SPICE netlists to Qucs netlist format. It was for example not possible to simulate Qucs models encoded in the Qucs netlist format directly with a SPICE simulator or to generate a Verilog-A code model directly from a Qucs EDD model. This situation will change significantly as the spice4qucs project moves forward: in the medium to long term a number of synthesis-translation routines will be added to Qucs making the process of model translation transparent to the Qucs user. The first of these is the link between the Qucs netlist format and the Ngspice, Xyce and SPICE OPUS simulator netlist formats. Figure 1.5 shows a Qucs tunnel diode EDD model, a DC swept parameter test circuit and a set of Ngspice simulation results. Figure 1.7 lists an Ngspice netlist generated automatically by spice4qucs for the circuit shown in Figure 1.5. Notice that this netlist is not simply a list of SPICE component statements but includes an embedded Ngnutmeg script between the SPICE **.control ... and .... endc** statements.

```

* Qucs 0.0.19

1

* Qucs 0.0.19 TD.sch

2

.SUBCKT TD _net0 _net1 VT=0.025 Is=1e-12 Ip=1e-5 Iv=1e-6 Vp=0.1 Vv=0.4 K=5 C=0.01p

3

BD110 _net0 _net1 I=Is*(exp((V(_net0)-V(_net1))/VT)-1.0)

4

GD1Q0 _net0 _net1 nD1Q0 _net1 1.0

5

LD1Q0 nD1Q0 _net1 1.0

6

BD1Q0 nD1Q0 _net1 I=-(C*(V(_net0)-V(_net1)))

7

BD1I1 _net0 _net1 I=Iv*exp(K*((V(_net0)-V(_net1))-Vv))

8

BD112 _net0 _net1 I=Ip*((V(_net0)-V(_net1))/Vp)*exp((Vp-(V(_net0)-V(_net1)))/Vp)

9

. ENDS

10

_net0 0 TD VT=0.025 Is=1E-12 Ip=1E-5 Iv=1E-6 Vp=0.1 Vv=0.4 K=5 C=0.01P

XTD2

11

VI_TD1 _net1 _net0 DC 0 AC 0

12

V1 _net1 0 DC 0.1

13

.control

14

set filetype=ascii

15

```

```

16 DC V1 -0.05 0.4 0.000997783

17 write _dc.txt VI_TD1#branch

18 destroy all

19 exit

20 .endc

21 .END

```

Figure 1.7. A synthesized Ngspice netlist for the tunnel diode circuit shown in Figure 1.5.

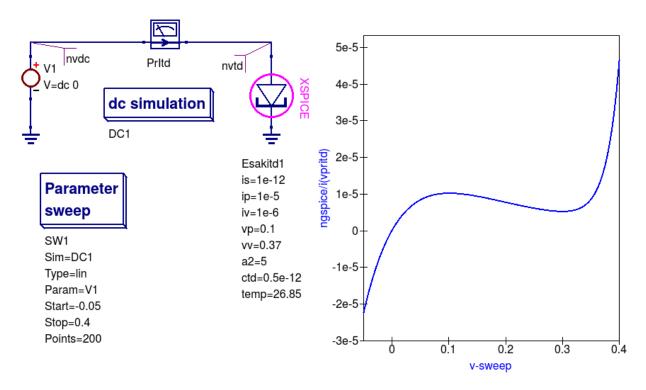

Figure 1.8, and the associated model code, introduce a user defined XSPICE Code Model for the tunnel diode example. A recent extension to the spice4qucs compact device modelling capabilities adds a "turn-key" feature which allows user defined XSPICE Code Models to be added to Qucs and automatically compiled to C code by the package. More on this topic and all the others introduced earlier in this chapter can be found in later sections of this document.

Figure 1.8. XSPICE Code Model tunnel diode model, test circuit and Ngspice simulation results.

```

/*

etd cm model.

2

3

2 April 2016

Mike Brinson

4

5

6

This is free software; you can redistribute it and/or modify

7

it under the terms of the GNU General Public License as published by

8

9

the Free Software Foundation; either version 2, or (at your option)

any later version.

10

*/

11

12

13

#include <math.h>

14

15

```

```

void cm_etd(ARGS)

16

17

{

Complex_t ac_gain1;

18

static double PVP, PIP, PVV, PIV, PA2;

19

static double PIS, T2, con1, con2, con3, VT;

20

double ith, ix, it, dith, dix, ditu;

21

static double vtd, itd, diff;

22

double P_K, P_Q;

23

24

if (INIT) {

25

PVP

= PARAM(vp);

26

27

PIP

= PARAM(ip);

PVV

= PARAM(vv);

28

PIV

= PARAM(iv);

29

PA2

= PARAM(a2);

30

PIS

= PARAM(is);

31

32

/*

*/

33

Constants

34

/* Boltzmann's constant in J/K */

P_K

= 1.3806503e-23 ;

35

/* Charge of an electron in C */

P_Q

= 1.602176462e - 19;

36

Т2

= PARAM(temp)+237.15;

37

/\,\star\, Thermal voltage at Temp in volts \,\star\,/\,

VT

= P_K \star T2/P_Q;

38

= PIV*PA2;

39

con1

40

con2

= PIS/VT;

41

con3

= PIP/PVP;

42

43

44

}

45

46

if (ANALYSIS != AC) {

47

vtd = INPUT(ntd);

48

ith = PIS*(exp(vtd/VT) -1.0);

49

ix

= PIV*exp(PA2*(vtd-PVV));

50

it

= PIP*(vtd/PVP)*exp(1-vtd/PVP);

51

itd = ith+ix+it;

52

53

dith = con2*exp(vtd/VT);

54

dix = con1*exp(PA2*(vtd-PVV));

ditu = con3*(1-vtd/PVP)*exp(1-vtd/PVP);

55

diff = dith+dix+ditu;

56

57

OUTPUT(ntd) = itd;

58

PARTIAL(ntd, ntd) = diff;

59

60

}

61

62

else {

63

ac_gain1.real = diff;

64

ac_gain1.imag = 0.0;

65

66

AC_GAIN(ntd, ntd) = ac_gain1;

67

}

68

69

70

}

```

# Chapter 2. Basic Ngspice, Xyce and SPICE OPUS simulation

#### 2.1 Introduction

This section describes a number of fundamental methods for launching circuit simulations from the Qucs GUI using the Ngspice, Xyce and SPICE OPUS compatible simulator engines. Spice4qucs includes built-in support for SPICE via a subsystem specifically designed for this purpose. The Ngspice, Xyce and SPICE OPUS simulators are not embedded in Qucs but operate as independent external simulators. Before use they must be installed on the computer operating system that you are running Qucs.

#### 2.2 Supported simulators

Ngspice is a mixed-level/mixed-signal circuit simulator implemented from three open source software packages: SPICE 3f5, Cider 1b1 and XSPICE. Ngspice is one of the most widely used and stable current generation open source SPICE simulators available. It implements the original SPICE3f5 simulation capabilities, including for example, DC, AC, and transient simulation, Fourier-analysis and sensitivity analysis, plus a significant number of extra simulation and device model extensions. Distributed with Ngspice is a data manipulation package called Ngnutmeg. This provides numerical analysis and visualisation routines for post processing Ngspice simulation data. Instructions for installing Ngspice can be found on the Ngspice website at http://ngspice.sourceforge.net/download.html, The Ngspice website also gives free access to all the distribution and development package code sources.

Xyce is an open source, SPICE-compatible, high-performance analogue circuit simulator, capable of solving extremely large circuit problems when installed on large-scale parallel computing platforms. It also supports serial execution on all common desktop platforms, and small-scale parallel execution on Unix-like systems. Xyce for Linux, Microsoft Windows, and MacOS can be downloaded from the official Xyce website at https://xyce.sandia.gov/Xyce. The Xyce parallel circuit simulator running on Linux requires installation of the openMPI libraries. Spice4qucs supports both Xyce-Parallel (not currently available for the Microsoft Windows operating system).

SPICE OPUS is an improved version of SPICE based on the original SPICE 3f5 code with extensions for circuit and device performance optimization and a transient simulation shooting method for large signal steady state AC analysis. SPICE OPUS can be downloaded from its official website at http://www.spiceopus.si/.

Although Ngspice, Xyce and SPICE OPUS are all compatible SPICE simulators they also include extensions to the original SPICE 3f5 netlist syntax which are often incompatible and may not simulate but generate errors. The Ques Team is aware of this limitation and are attempting to correct such problems as quickly as possible. Please note this may take some time. However, if you do identify a compatibility bug please inform us by sending in a bug report to the Ques web site (with an example test schematic if possible) describing the problem you have identified.

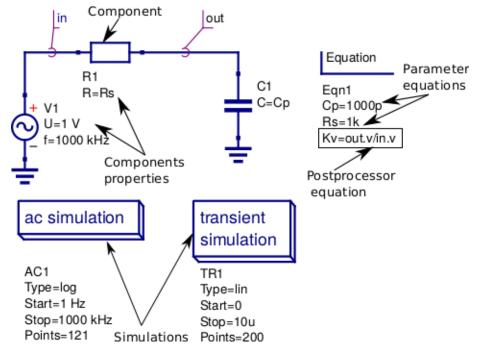

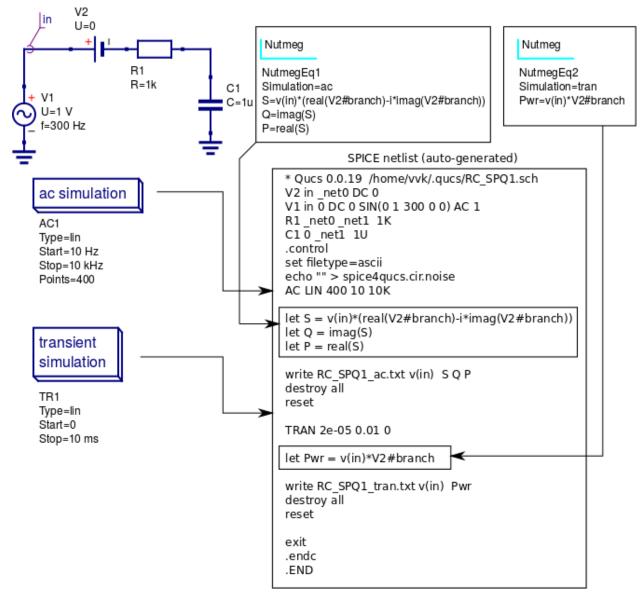

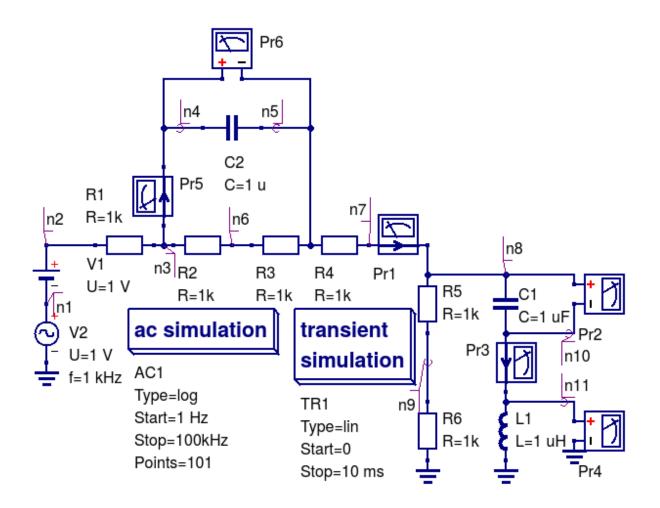

#### 2.3 General simulation methods

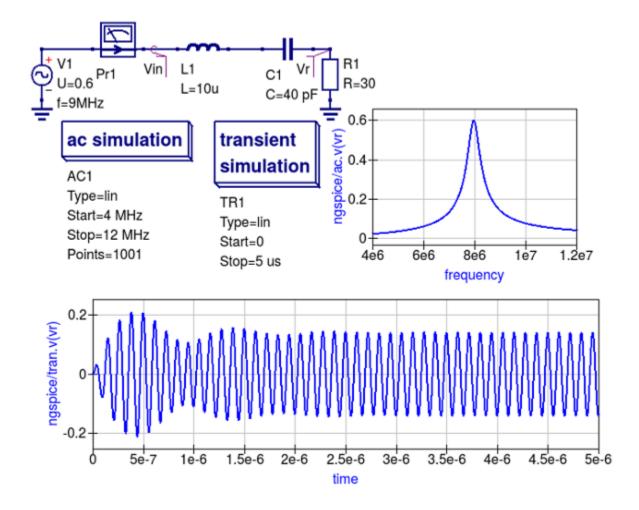

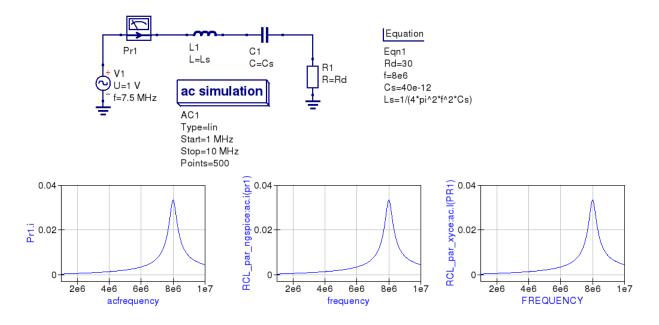

The starting point for understanding how the spice4qucs extensions are built into the Qucs GUI is to study the basic operations needed to simulate Qucs circuit schematics with external simulators. For this purpose consider the simple RCL circuit shown in Figure 2.1.

Figure 2.1. A simple RCL test circuit for demonstrating Ngspice, Xyce and SPICE OPUS simulation controlled from Ques.

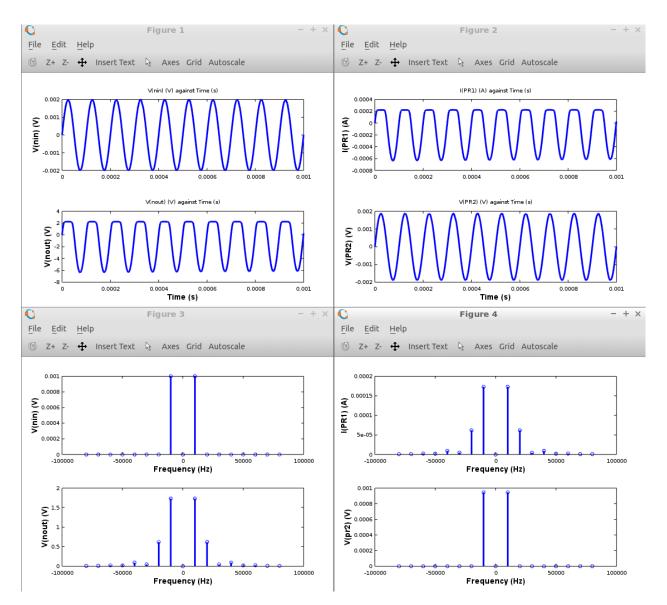

This schematic specifies two simulations:

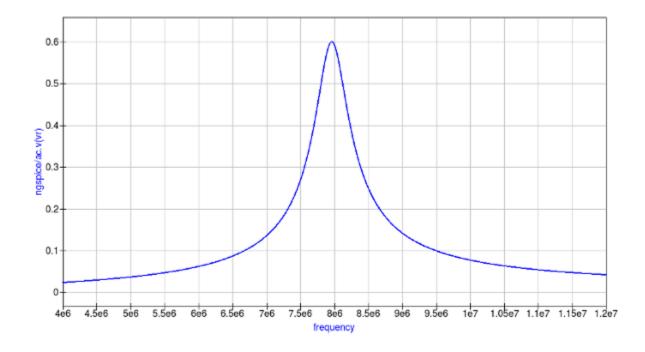

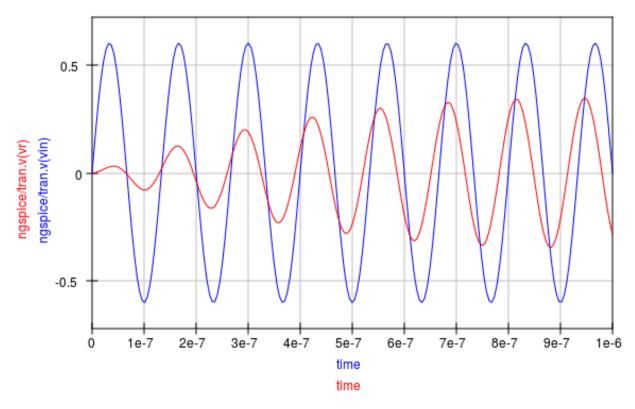

- AC simulation from 4 MHz to 12 MHz.

- Transient simulation from 0 to 5 us;

Make sure the schematic in Figure 2.1 is drawn correctly then simulate it with Quesator using the sequence *Simulation-Simulate*, or by pressing key F2. After Ques finishes the the AC and transient simulations, plot the output data listed below:

- The voltage across R1 resistor in the frequency domain (given by the voltage at the Vr node ),

- The input and output voltage waveforms (the voltages given by the Vin and Vr nodes ) your plots should be similar to those shown in Figure 2.1,

- The current in the frequency domain (Prl current probe ),

- The transient current waveform sensed by the current probe Pr1.

Spice4qucs allows schematic component properties to be defined in the same way as Qucs. Component values and other icon properties are converted automatically into SPICE compatible netlist format. There is no need for manual adaptation by users. However, please note that not all the predefined Qucs components are available for simulation with Ngspice, Xyce or SPICE OPUS. A number of tables provided in later sections of the text list which components

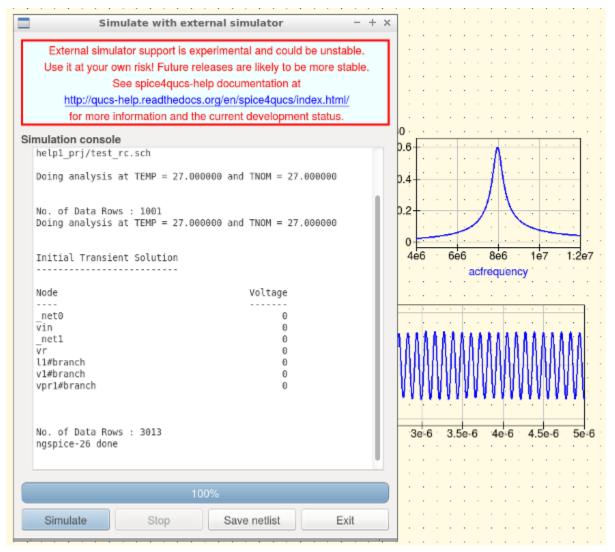

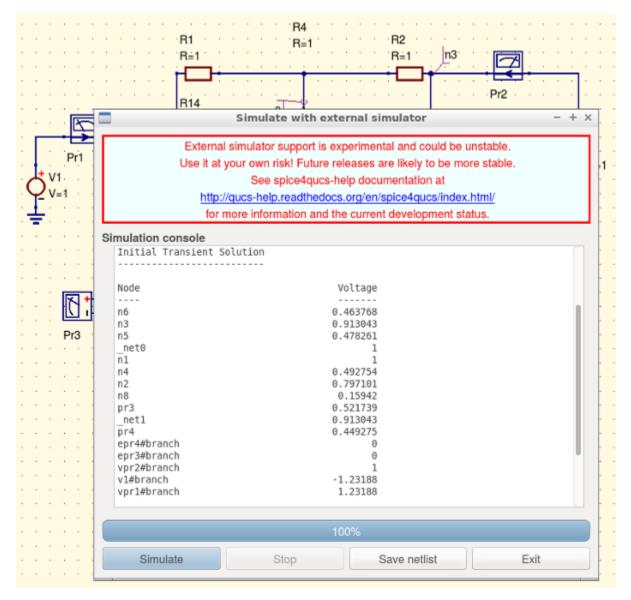

can be used with which simulator. Following placement and wiring of components, plus the addition of one or more simulation icons, SPICE simulation is launched using the Ques menu sequence *Simulation -> Simulate* or by pressing key F2. An *External simulator* dialogue then appears. This is illustrated in Figure 2.2.

| Simulate with external simulator - +                                                                                                                                                                                                                                                                                 |                                                                         |                    |      |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|------|--|

| External simulator support is experimental and could be unstable.<br>Use it at your own risk! Future releases are likely to be more stable.<br>See spice4qucs-help documentation at<br><u>http://qucs-help.readthedocs.org/en/spice4qucs/index.html/</u><br>for more information and the current development status. |                                                                         |                    |      |  |

| Simulation console                                                                                                                                                                                                                                                                                                   | Solution                                                                |                    |      |  |

| Node<br>net0<br>vin<br>net1<br>vr<br>ll#branch<br>vprl#branch<br>vprl#branch                                                                                                                                                                                                                                         | Voltage<br><br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |                    |      |  |

| Simulate                                                                                                                                                                                                                                                                                                             | 100<br>Stop                                                             | 0%<br>Save netlist | Exit |  |

Figure 2.2. External simulator dialogue: where button *Simulate* launches a circuit simulation, button *Stop* causes a running simulation to finish; button *Save netlist* generates, and stores, the netlist of the circuit being simulated and button *Exit* closes the external simulator dialogue.

If the Ngspice, Xyce or SPICE OPUS installation directories are not included in the operating system shell <code>\$PATH</code> statement the location of their executable code must be registered with <code>spice4qucs</code> before Ngspice Xyce or SPICE OPUS simulations will work. This step is necessary for all the operating systems used to run <code>spice4qucs</code>. To register external circuit simulator installation directories <code>spice4qucs</code> users need to launch the *Select default simulator*, from the *Simulate* dialogue. The resulting *Setup simulators executable simulator location* dialogue is illustrated in Figure 2.3. Using this dialogue enter the absolute address of the Ngspice, Xyce or SPICE OPUS executable program code from the keyboard or by pressing the appropriate *Open File Select button*.. In the case of the Xyce Parallel simulator the number of processors installed in your computer system, must also be entered from the keyboard or selected using the dialogue up-down arrow controls.

| Setup simulators executable location - + ×                     |  |  |  |  |  |

|----------------------------------------------------------------|--|--|--|--|--|

| Default simulator Ngspice ‡                                    |  |  |  |  |  |

| Ngspice executable location                                    |  |  |  |  |  |

| /usr/local/bin/ngspice Select                                  |  |  |  |  |  |

| Xyce executable location                                       |  |  |  |  |  |

| Xyce-Release-6.2.0-OPENSOURCE/bin/runxyce Select               |  |  |  |  |  |

| Xyce Parallel executable location (openMPI installed required) |  |  |  |  |  |

| se-6.2.0-OPENMPI-OPENSOURCE/bin/xmpirun Select                 |  |  |  |  |  |

| Number of processors in a system: 4                            |  |  |  |  |  |

| SpiceOpus executable location                                  |  |  |  |  |  |

| /usr/local/bin/spiceopus Select                                |  |  |  |  |  |

| Directory to store netlist and simulator output                |  |  |  |  |  |

| /home/mike/spice4qucs Select                                   |  |  |  |  |  |

| Apply changes Cancel                                           |  |  |  |  |  |

Figure 2.3. Setup simulator executable locations dialogue.

Please note the Xyce parallel command line for binary Xyce-Parallel package has the following format:

<Path\_to\_xyce\_executable>/xmpirun -np %p

Where spice4qucs substitutes the number of processors for the %p wildcard entry.

Also please note that "user builds" of Xyce-Parallel have no xmpirun script, implying that the full script must be completed by users during the external simulators set up process, for example if <code>opeMPI</code> is installed in directory /usr/bin and Xyce-Parallel installed in /usr/local/Xyce\_Parallel the command line will be:

/usr/bin/mpirun -np %p /usr/local/Xyce\_Parallel/bin/Xyce

Spice4qucs users can also define a directory where temporary simulator data and netlists are stored: this simulator working directory is by default assumed to be at \$HOME/.qucs/spice4qucs.

To simulate a Ques schematic with the Ngspice simulator, select simulator *Ngspice* and press the *Simulate* button shown in Figure 2.2. During simulation Ngspice produces a simulation log. This is displayed in the *External simulator* dialog window, see Figure 2.4. The Ques Log text is also saved at Ques system Log location HOME/.ques/log.txt. The Log text can be viewed and using the drop down menue sequence *Simulation->Show last messages* (or by pressing key F5). If the Ngspice simulation fails, any errors reported by Ngspice during simulation are listed in simulation Log window. Similarly, a successful completion of a Ques/Ngspice simulation is reported.

Figure 2.4. A section of an Ngspice execution Log displayed in the *Simulate with an external simulator* dialogue window.

An novel feature introduced by spice4qucs is its ability to generate and save SPICE netlist files from the information contained in a Qucs schematic. To save the SPICE netlist file for the current simulation press the *Save netlist* button shown in Figure 2.2. This process causes a SPICE netlist to be saved as file "netlist.cir" in the ~/.qucs/spice4qucs directory. Here is the generated netlist for the RCL test example:

```

* Qucs 0.0.19 /home/vvk/qucs/examples/ngspice/RCL.sch

V1 _net0 0 DC 0 SIN(0 0.6 7.5MEG 0 0) AC 0.6

VPr1 _net0 vIn DC 0 AC 0

```

1

2

```

L1 vIn _net1 10U

4

R1 0 vR 30

5

C1 _net1 vR 40P

6

.control

7

set filetype=ascii

8

AC LIN 1000 4MEG 12MEG

9

write RCL_ac.txt VPr1#branch v(vIn) v(vR)

10

destroy all

11

TRAN 4.97512e-09 1e-06 0

12

write RCL_tran.txt VPr1#branch v(vIn) v(vR)

13

destroy all

14

exit

15

16

.endc

.END

17

```

The simulation sequence introduced in the previous sections of the spice4qucs-help text also applies to the Xyce and SPICE OPUS simulators. However, the information displayed in the simulation log is likely to be different for different simulators and indeed operating systems.

After an Ngspice, Xyce or SPICE OPUS simulation has successfully completed close the *External simulation* dialogue by pressing the "Exit" button. The simulation data generated by a spice4qucs simulation is available for plotting using the normal Qucs visualisation routines: either drag a diagram icon, or table icon, onto the current Qucs schematic window or onto the associated Qucs display page. After a diagram or table is placed a *Diagram properties* dialog appears. On selecting the dataset for the current simulation the simulation output quantities become available for plotting or tabulating in a similar fashion to standard Qucs.

|             |              |           | Edit Diagram | Proper | ties          |          |          |           | - + |

|-------------|--------------|-----------|--------------|--------|---------------|----------|----------|-----------|-----|

| Data Prope  | rties Limits |           |              |        |               |          |          |           |     |

| Graph Input |              |           |              |        |               |          | 1        |           |     |

|             |              |           |              |        |               |          | Plot Vs. | default   | :   |

| Color:      |              | Style:    | solid line   | ¢      | Thickness:    | 0 y-Axis | 5        | left Axis | 0   |

| Dataset     |              |           |              | Graph  |               |          |          |           |     |

| test_RC     |              |           | \$           | ngs    | pice/ac.v(vr) |          |          |           |     |

| Data from   | simulator:   | Ngspice   | \$           |        |               |          |          |           |     |

| Name >      | / Туре       | S         | ize          |        |               |          |          |           |     |

| ac.i(pr1)   | dep          | frequency |              |        |               |          |          |           |     |

| ac.v(vin)   | dep          | frequency |              |        |               |          |          |           |     |

| ac.v(vr)    | dep          | frequency |              |        |               |          |          |           |     |

| frequency   | indep        | 1001      |              |        |               |          |          |           |     |

| time        | indep        | 3013      |              |        |               |          |          |           |     |

| tran.i(pr1) | dep          | time      |              |        |               |          |          |           |     |

| tran.v(vin) | dep          | time      |              |        |               | New Gr   | aph      |           |     |

| tran.v(vr)  | dep          | time      |              |        |               | Delete G | raph     |           |     |

|             |              |           |              |        |               |          |          |           |     |

|             | OK           |           | A            | pply   |               |          | Canc     | el        |     |

Figure 2.5. *Diagram properties* dialogue, listing the selected simulator and the available simulation data names.

Ngspice, Xyce and SPICE OPUS simulation data output is in raw-binary SPICE 3f5 output format. Ques converts the SPICE 3f5 style data into a Ques dataset using routines provided in the spice4ques Ques subsystem. Results from different types of simulation, for example SPICE AC and TRAN, are combined into a single Ques dataset. Ques adds an appropriate suffix to each simulator dataset name in order to avoid name clashes and mixing up results from different types of simulation. In the RCL test example the Ques schematic is named RCL.sch. Ques quesator simulation, Ngspice, Xyce and SPICE OPUS simulations result in three different datasets:

- RCL.dat for Quesator;

- RCL.dat.ngspice for Ngspice;

- RCL.dat.xyce for Xyce;

- RCL.dat.spopus for SPICE OPUS;

All four datasets have an extension dat to signify that each set contains Ques data for post simulation visualisation. The Ngspice, Xyce and SPICE OPUS datasets include second a extension to the file name to identify the name of the external Ques simulator.

The Dataset selector (see Figure 2.5) shows only the base names of a dataset (for example test\_RC). Users must also select the appropriate simulator from the *simulator name selector* drop-down list. This drop-down only gives existing simulator datasets which prevents users from selecting non-existent datasets by mistake.

Following the selection of a specific data set users must select the variables that are to be plotted. Spice4qucs preserves SPICE notation for **node voltage** names and **current probe** names. SPICE names are assumed to be case insensitive by spice4qucs, for example

- v(out) Voltage at node out;

- i (Pr1) Current recorded by current probe Pr1;

The Ques spice4ques extension also adds a simulation-dependent prefix to each variable name in order to differentiate output variables from different SPICE simulations, for example ac. for AC simulation, tran. for transient simulation, and dc. for DC-sweep.

There are also individual prefixes for each simulator:

- ngspice/ Ngspice simulator prefix;

- xyce/ Xyce simulator prefix;

- spopus/ SPICE OPUS prefix;

Hence for example, the full name of variable from an Ngspice simulation could be ngspice/v(out) This naming system helps to avoid dataset name conflicts.

Individual items for plotting are selected by double clicking on a name in the variable list. As an example when double clicking on ac.i(prl) its name is copied by Qucs into the right-hand plotting window. Like standard Qucs one or more variable items may be selected for plotting on the same 2D or 3D graph. Finally pressing the *Apply* button shown at the bottom of Figure 2.5. causes the selected variable items to be plotted. The plotted simulation results for the external Ngspice AC simulation of the RCL test circuit are shown in Figure 2.6.

Figure 2.6. External SPICE AC simulation magnitude response for the current flowing in RCL circuit with a series resonant peak of roughly 8 MHz.

Plotting the transient simulation data for the RCL test example follows the same procedure as the sequence described for the AC simulation except that in the transient plot variables with tran in their name are selected, see Figure 2.7.

Figure 2.7. Transient simulation voltage waveforms at the input and output nodes of the RCL circuit.

A similar proceedure is adopted for plotting simulation data generated with the Xyce and SPICE OPUS simulators. Readers should make sure they can simulate the example RCL circuit with both Xyce and SPICE opus, then plot the resulting simulation data. More advanced techniques for post processing, plotting and undertaking a range of different visualization processes using Qucs and Octave are outlined in chapter 7.

#### 2.4 Variable names

As part of the spice4qucs extensions Ngspice and Xyce simulation variable names are converted from Qucs notation to SPICE notation and vica versa. Table 2.1 shows the correspondence between the two notations.

| Variable type      | Qucs display notation | Spice display notation |

|--------------------|-----------------------|------------------------|

| DC node voltage    | Node.V                | V(node)                |

| AC node voltage    | Node.v                | ac.v(node)             |

| TRAN node voltage  | Node.Vt               | tran.v(node)           |

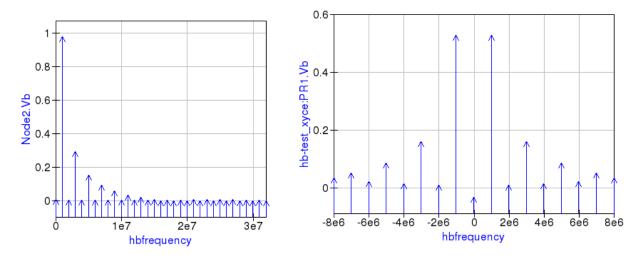

| HB node voltage    | Node.Vb               | hb.v(node)             |

| DC probe current   | Pr1.I                 | i(pr1)                 |

| AC probe current   | Pr1.i                 | ac.i(pr1)              |

| TRAN probe current | Pr1.It                | tran.i(pr1)            |

Table 2.1 Qucs and SPICE variable equivalences

Also variable prefixes used to designate data from different simulators (Table 2.2)

Table 2.2 Qucs and SPICE variable name prefixes

| Prefix                                  | Explanation                             |

|-----------------------------------------|-----------------------------------------|

| Node.Vt                                 | Qucs simulation, default dataset        |

| dataset:Node.Vt                         | Ques simulation, external dataset       |

| ngspice/tran.v(node)                    | Ngspice simulation, default dataset     |

| <pre>ngspice/dataset:tran.v(node)</pre> | Ngspice simulation, external dataset    |

| xyce/tran.v(node)                       | Xyce simulation, default dataset        |

| xyce/dataset:tran.v(node)               | Xyce simulation, external dataset       |

| spopus/tran.v(node)                     | SPICE OPUS simulation, default dataset  |

| <pre>spopus/dataset:tran.v(node)</pre>  | SPICE OPUS simulation, external dataset |

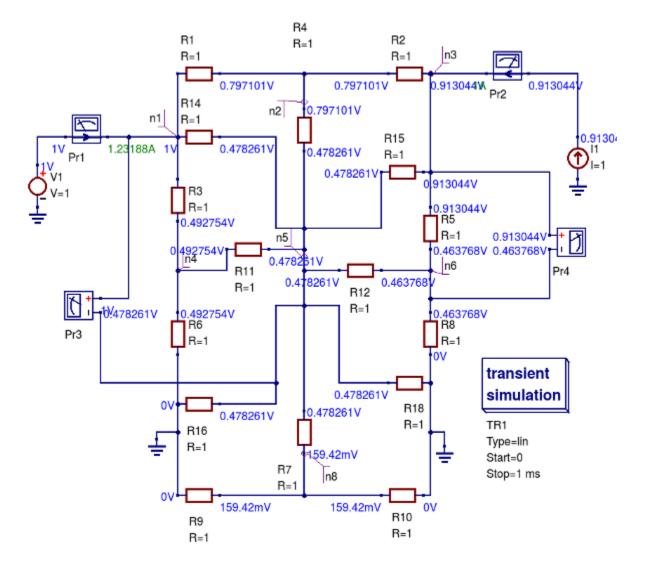

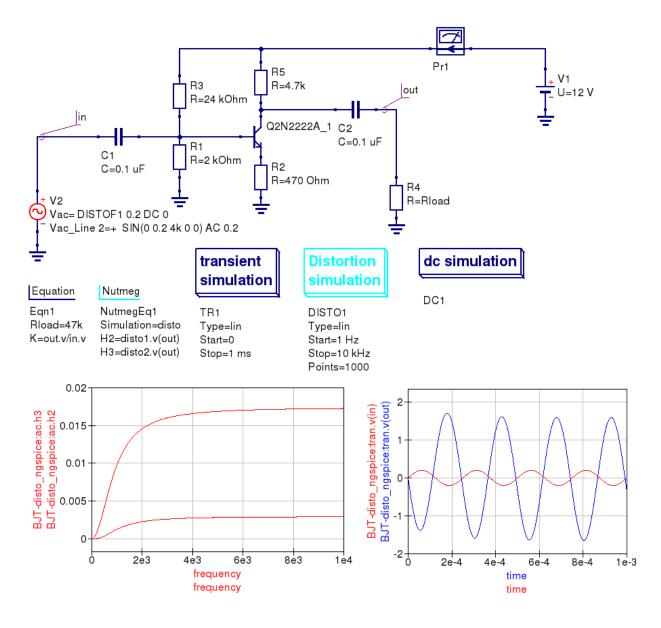

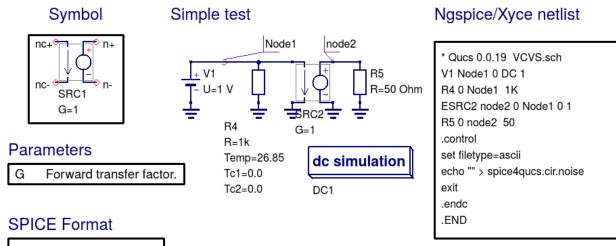

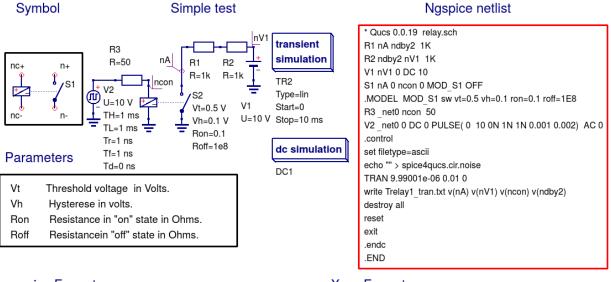

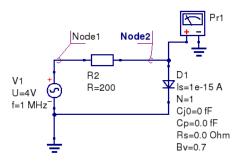

#### 2.5 DC simulation

Conventional SPICE 3f5 simulation commands OP and DC are not implemented by Qucs or indeed by spice4qucs. Instead more convenient versions of these simulation commands are implemented. These alternative forms of nonlinear steady state DC circuit analysis are linked directly to circuit schematic capture, making them easy to use. Moreover, they provide spice4qucs users with a power full diagnostic and analysis tools for investigating basic circuit operation. The circuit shown in Figure 2.8 represents a simple resistive network with single voltage and current 1 V and 1 A sources respectively. Pressing key "F8" instigates a DC analysis and adds the DC node voltages, probe voltages and probe currents to the current schematic. This feature provides a practical method for scanning a circuit to see if the DC bias values are of the correct order of magnitude. The calculation of DC bias values via the F8 key applies to all the circuit simulators controlled by spice4qucs. Schematics which include the spice4qucs DC icon do not however, list a similar set of voltage and currents in the \*Simulate with an external Simulator" dialogue window. A DC voltage and current list is output when a schematic includes a transient simulation icon, see Figure 2.9.

Figure 2.8 A simple linear resistive electrical network driven by single DC voltage and current sources: DC node voltages (V) and voltage probe values (V) are illustrated in blue and current probe values (A) in green.

Figure 2.9 A screen dump showing transient simulation initial DC simulation voltage and current values in (V) and (A) respectively for the resistive circuit given in Figure 2.8: NOTE that the voltage and current variable names are output in SPICE style syntax.

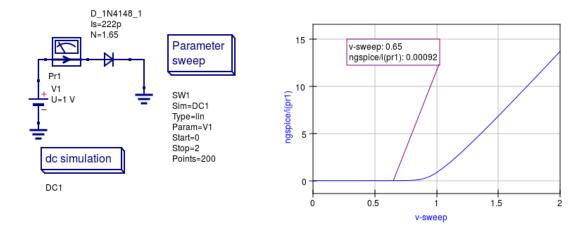

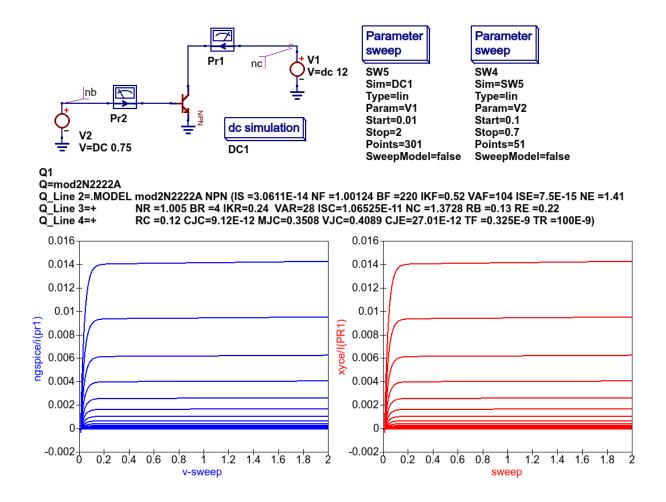

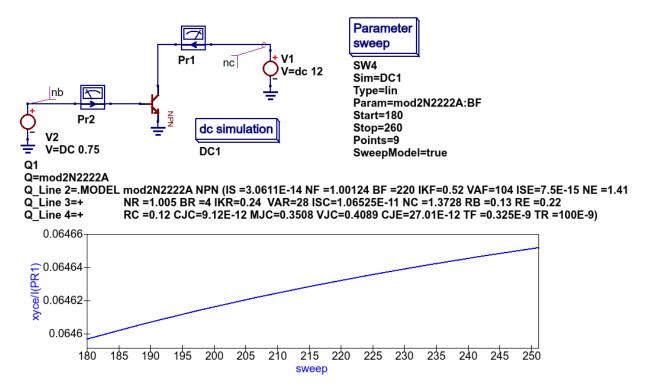

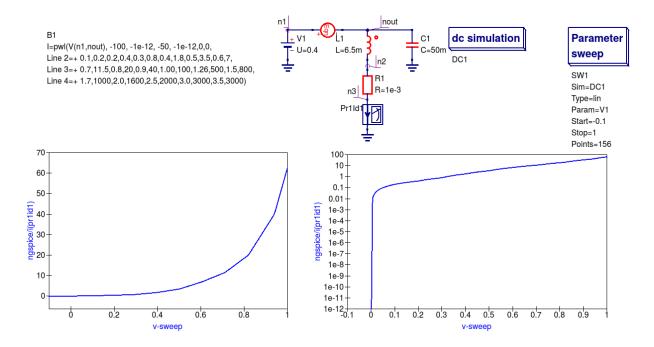

Ques does not define a separate analysis type which is equivalent to the original SPICE 2g6 "DC sweep" simulation or the extended SPICE 3f5 version which allows current and voltage source scans plus resistor value scans. In contrast to SPICE the Ques equivalent "DC sweep" is just a specific case of the more general Ques Parameter sweep capability. To emulate the original SPICE *DC sweep* 'spice4ques use a combination of Ques DC simulation plus the Parameter sweep of an independent DC voltage or DC current source or of a resistor numerical value; when the spice4ques Spice netlist builder finds these two linked types of simulation it synthesises them into a DC SPICE netlist entry. This procedure is demonstrated in Figure 2.10. where the test circuit consists of a diode DC bias network connected as a test bench for simulating the non-linear DC current-voltage characteristic of a 1N4148 diode. This example can be found in the Ques examples directory tree listed as examples/ngspice/diode.sch.

Figure 2.10. Test circuit and simulated DC current-voltage characteristics for a 1N4148 silicon diode.

PLease note the following differences between SPICE and Ques DC-sweep simulation:

- Specify a sweep source name or a resistor name NOT a source or resistor value; for example in Figure 2.10 V1.

- SPICE model parameters can be swept using the notation Device.Param, for example T1.Bf to sweep the Bf parameter of transistor T1.

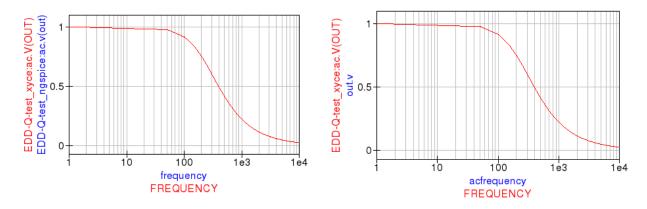

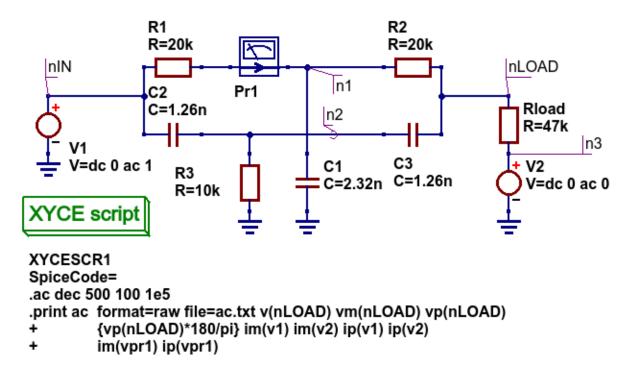

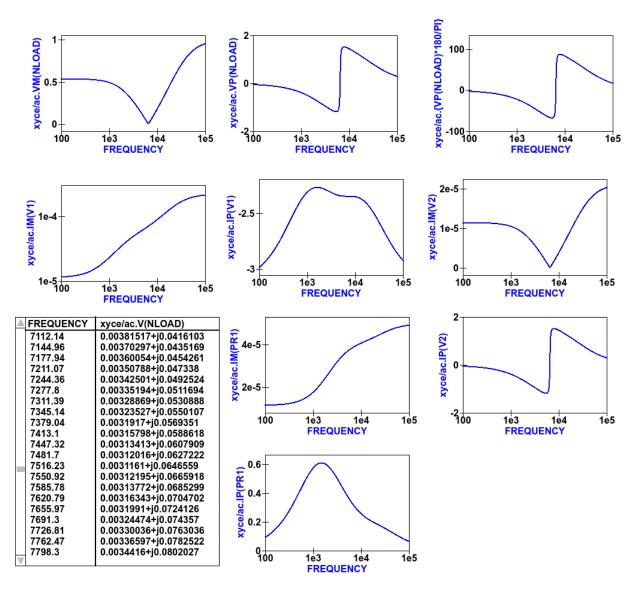

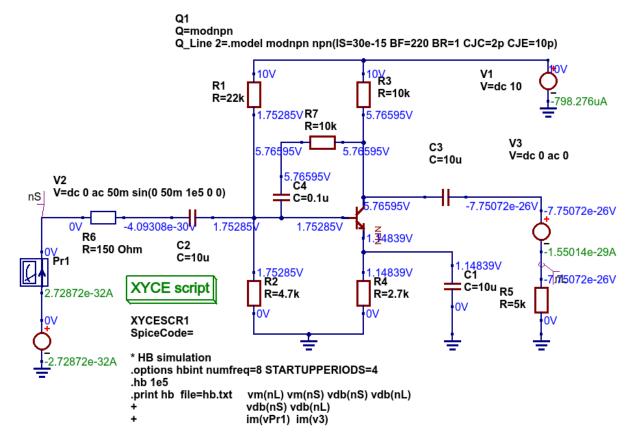

#### 2.6 AC simulation

Small signal AC simulation is fully supported by the spice4qucs subsystem. It doesn't require any special adaptation. Just simple place the AC simulation component icon on a schematic and execute an Ngspice, Xyce or SPICE OPUS simulation. Variable name conversions are listed in Table 2.1. The Qucs spice4qucs dataset builder adds the ac. prefix to all variables generated by an AC simulation.

Ngspice, Xyce and SPICE OPUS small signal frequency domain AC simulations use linear, decade or octave frequency scales. Adaptive frequency steps are not implemented.

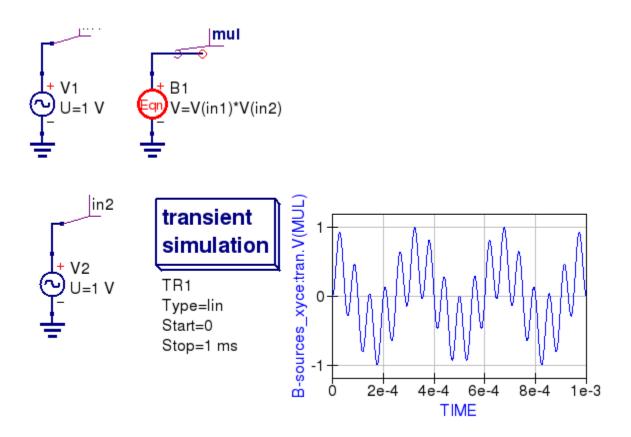

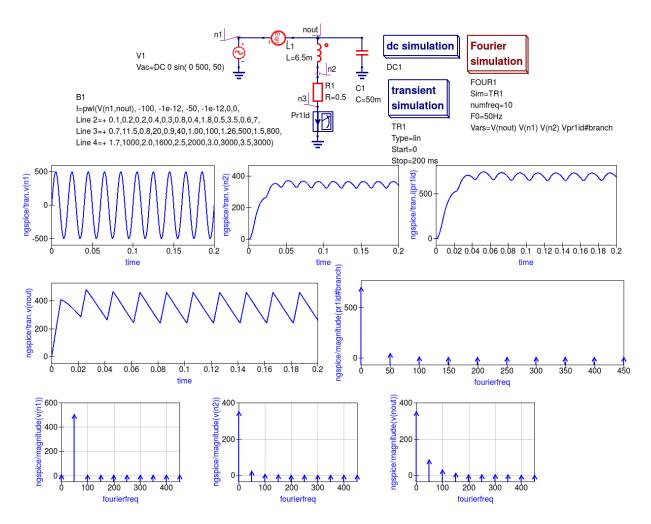

#### 2.7 TRANsient simulation

Transient simulation is also fully supported by the spice4qucs subsystem. Just place the Transient simulation component icon on a schematic and simulate it. There is a difference between the way the quesator, Ngspice, Xyce and SPICE OPUS simulators implement transient simulation time steps.

Quesator always uses a fixed time step. Ngspice, Xyce and SPICE OPUS use adaptive time steps. The number of simulation points output during a simulation will only be approximately equal to the number of simulation points specified in a Transient simulation properties list. For example, in an example test circuit 200 time points are specified on the schematic. However, due to the fact that the SPICE simulators use adaptive time steps, Ngspice employs 213 simulation points, and Xyce employs 799 time points. This difference should be taken into account during simulation data post processing and when comparing simulation results.

#### 2.8 Other forms of simulation

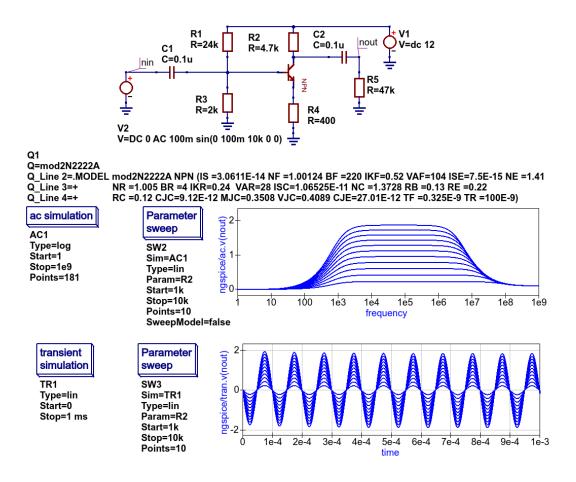

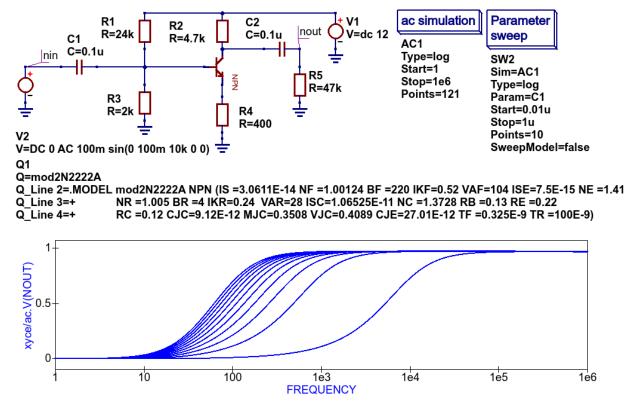

In contrast to SPICE 3f5, the parameter sweep facility found in Ques has also been implemented with Ngspice, Xyce and SPICE OPUS where the parameter sweep setup and control is organized by spice4ques. The details of how this Parameter sweep feature works is the topic of section 5.8.

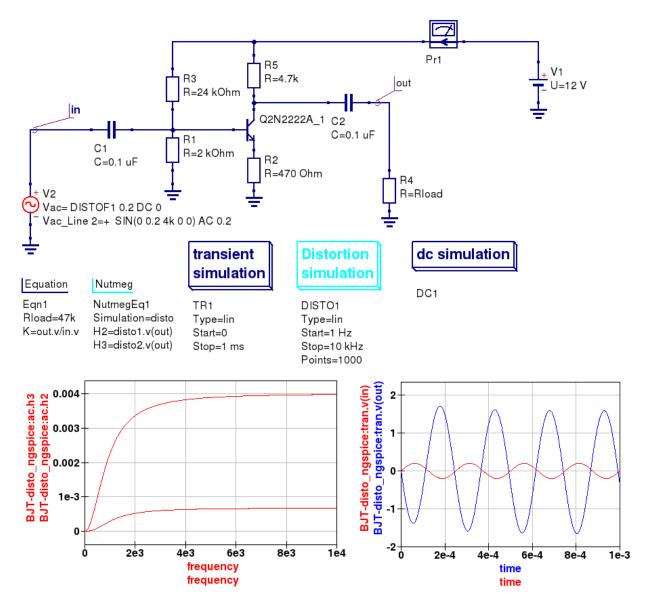

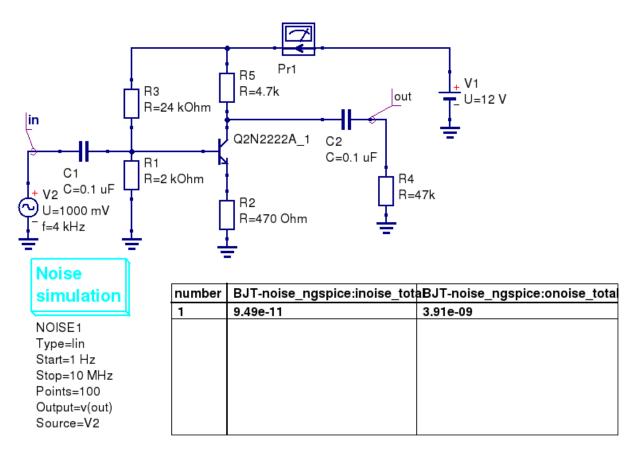

As well as the fundamental DC, AC and transient simulation types, Ngspice, Xyce and SPICE OPUS also support the additional forms of simulation listed in Table 2.3.

| Simulation Type      | Ngspice | Хусе | SPICE OPUS | See section |

|----------------------|---------|------|------------|-------------|

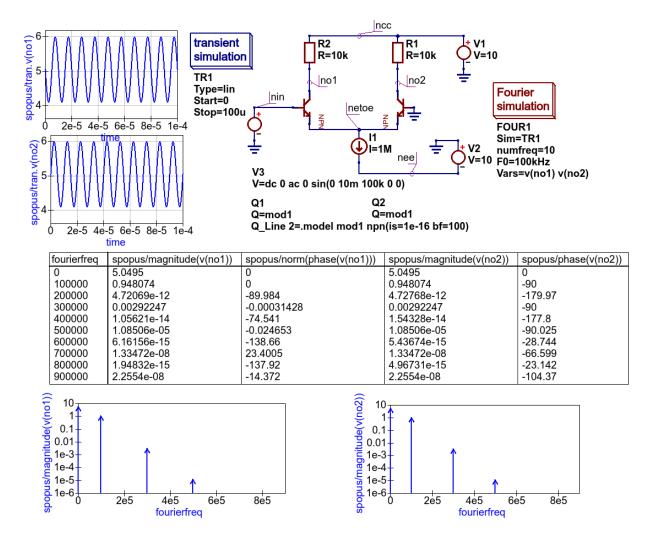

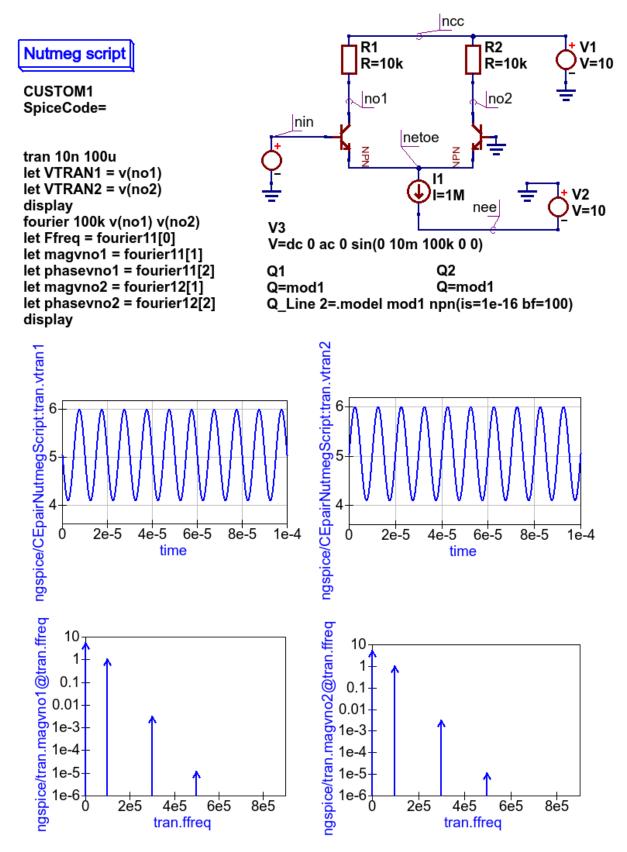

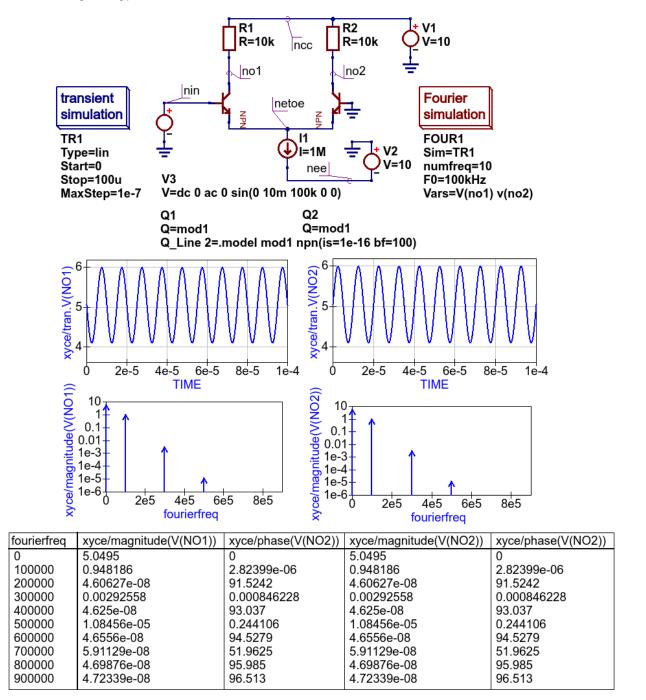

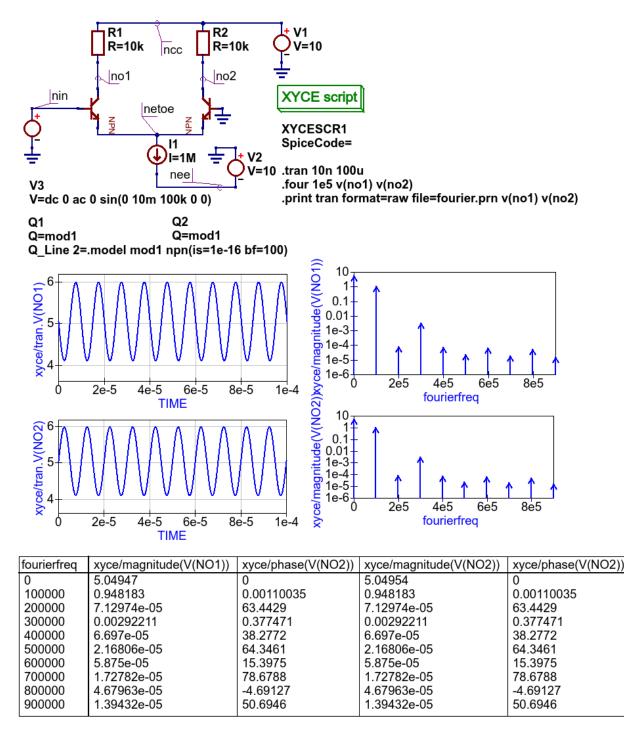

| Fourier              | Х       | Х    | Х          | 5.1         |

| Distortion           | Х       |      | Х          | 5.2         |

| Noise                | Х       | Х    | Х          | 5.3         |

| Pole-zero            | Х       |      | Х          | 5.4         |

| Sensitivity          | Х       | Х    | Х          | 5.5         |

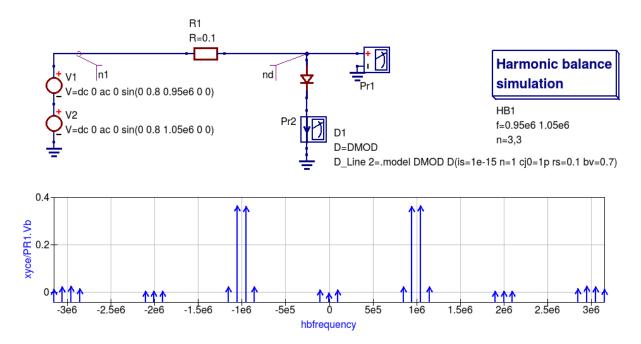

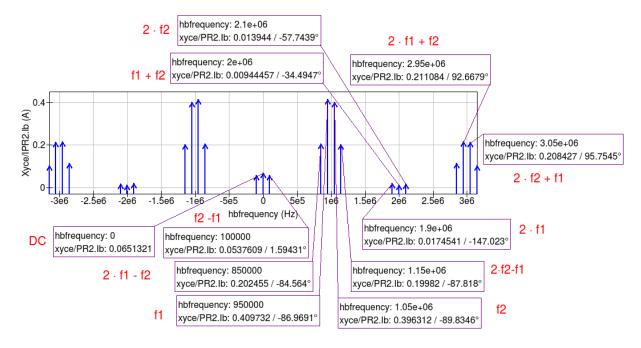

| Harmonic Balance     |         | Х    |            | 13.5        |

| Tran shooting method |         |      | Х          | 13.7        |

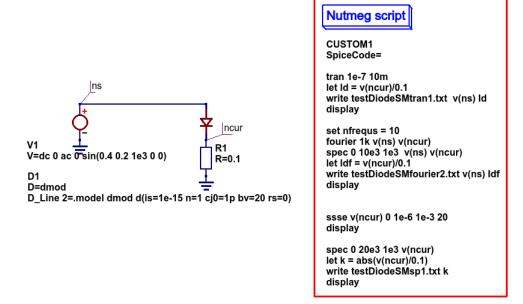

| Custom simulation    | Х       |      | Х          | 8.0         |

Table 2.3 Spice4qucs simulation types additional to DC, AC and TRAN

Fourier, distortion pole-zero circuit simulation require special GUI icons. These can be found in the Ques *Spice simulations* group. In contrast sensitivity, the SPICE OPUS tran shooting method is accessed by spice4ques via the Custom simulation technique, see section 8.0.

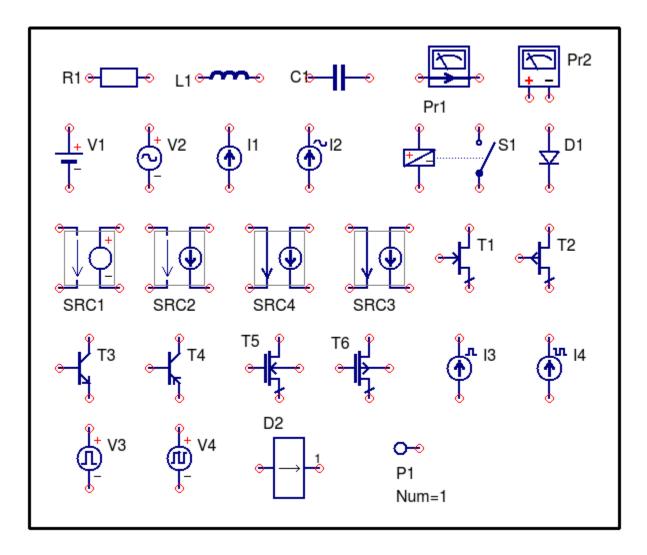

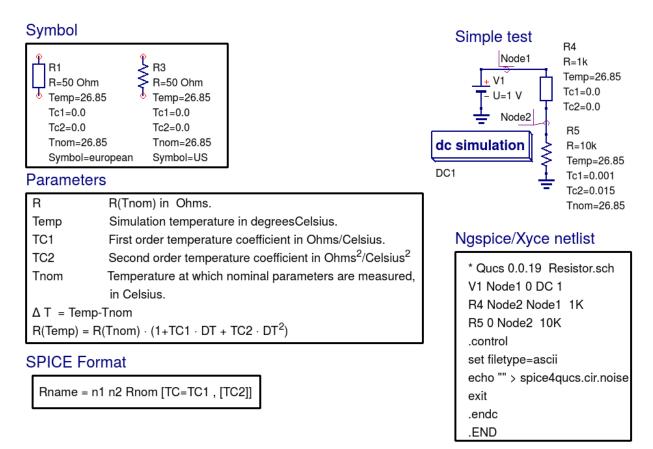

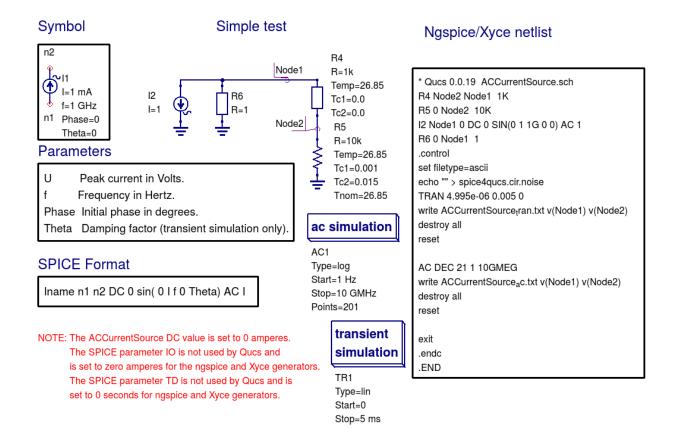

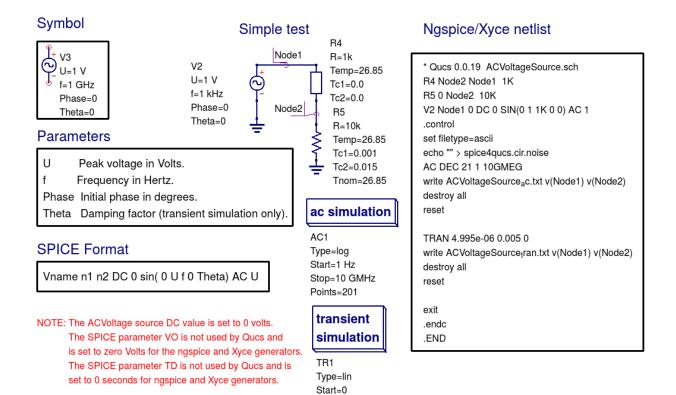

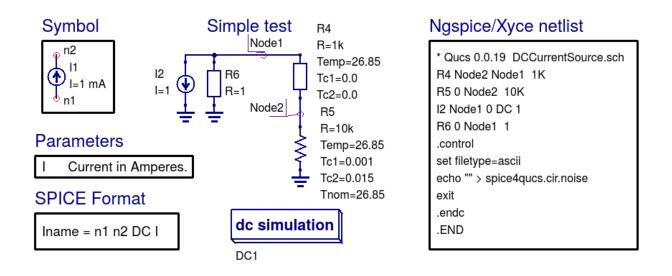

#### 2.9 Spice4qucs circuit simulation components

Ques is released with a good selection of passive and active component models. This selection includes both fundamental circuit components, like R, C and L and collections of specific components for a given circuit design sector, like the RF microstrip component models. All the original Ques component and device models were written to work with Ques and there is **NO Guarantee** that they will be work with Ngspice, Xyce or SPICE OPUS. For circuit simulation packages which take advantage of simulation multi-engines this can be a serious problem, particularly for the less experienced user. To help reduce problems to a minimum, spice4ques uses a policy of "blacklisting" those models which do not work with the chosen circuit simulation engine. This policy works in the following way:- when a specific simulator is chosen by a Ques spice4ques user, on running the chosen simulator, **ONLY** those models which work with the selected simulator become available for drawing circuit schematics and simulation. The same approach applies to the components held in the spice4ques libraries.

#### 2.10 More basic simulation examples

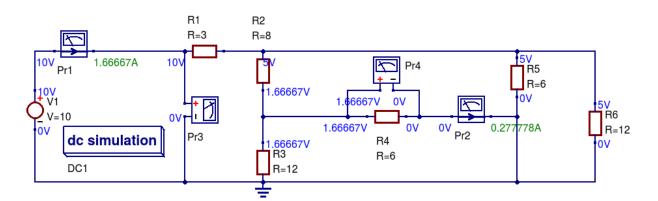

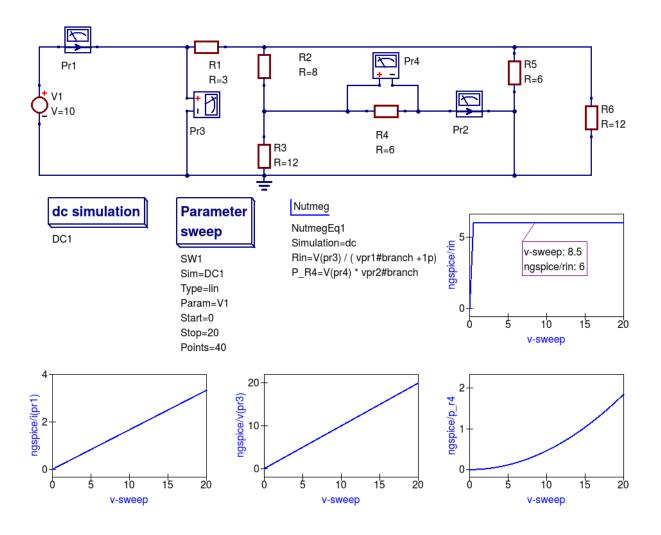

Figure 2.11 DC resistive test network.

• Draw the circuit diagram shown in Figure 2.11,

- Select simulator Ngspice,

- Press key F8

- Determine DC Rin = V(Pr3)/I(Pr1) = 10/1.66667 = 6 Ohm,

- Determine the power dissipated in R4 = V(Pr4)\*I(Pr2) = 1.66667\*0.277778 = 0.463 W.

#### 2.10.2 DC Example 2: Variation of power dissipation with varying DC input voltage.

Figure 2.12 DC example 1 with varying DC input voltage: demonstrating the use of a DC sweep simulation.

- Draw the circuit diagram shown in Figure 2.11,

- Select simulator Ngspice,

- Add the dc simulation, Parameter sweep and Nutmeg component icons to the drawn schematic,

- Complete the Parameter sweep and Nutmeg component data entries so that they are the same as given in Figure 2.11,

- Press the F2 to simulate the circuit,

- Plot the graphs illustrated in Figure 2.11,

• Check that your results are the same - if not or the simulation fails check your schematic for errors and resimulate.

Notes:

- Current probe values are represented by the SPICE 3f5 notation: vpr1#branch and vpr2#branch.

- There is a discontinuity in Rin when the vpr1#branch current is zero Amperes; hence the need for the dummy 1pA in the Nutmeg equation for Rin.

back to the top

## Chapter 3. Spice4qucs subcircuits, macromodels and device libraries

#### 3.1 Spice4qucs Subcircuits: with and without parameters

Subcircuits are a concept that has been part of established circuit simulation practice since the early days of computer aided circuit design. Today, all practical circuit simulators have subcircuits as part of their basic device compliment. This is not surprising because they form a natural way of breaking an electonic system down into a number of smaller self contained functional blocks. Spice4qucs supports all the features available with Qucs subcircuits. In a similar fashion to Qucs, the Ngspice, Xyce and SPICE OPUS circuit simulators allow subcircuits with or without parameters. However, an optional part of the Ngspice, Xyce and SPICE OPUS subcircuit netlist syntax that signifies that a parameter extension is present is not allowed (see section 3.1.2). As a starting point spice4qucs subcircuits without parameters are considered first. This introduction is followed by a detailed description of the structure, and netlist syntax, of subcircuits with one or more parameters.

#### 3.1.1 Spice4qucs subcircuits without parameters

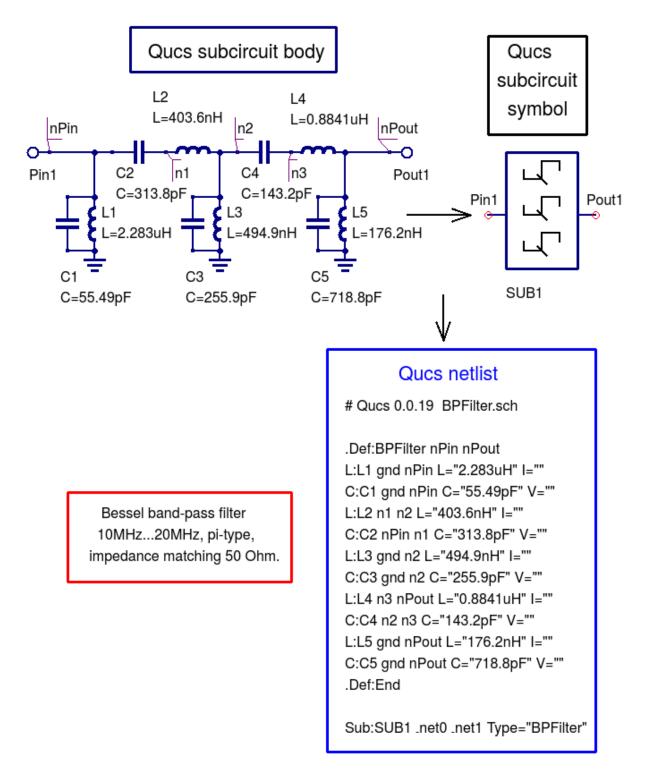

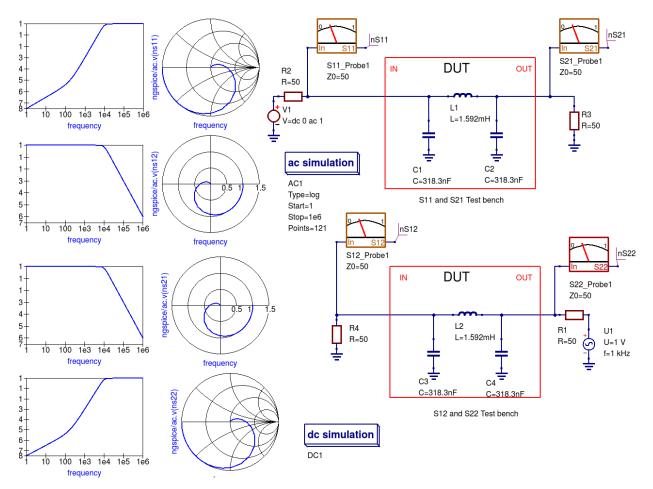

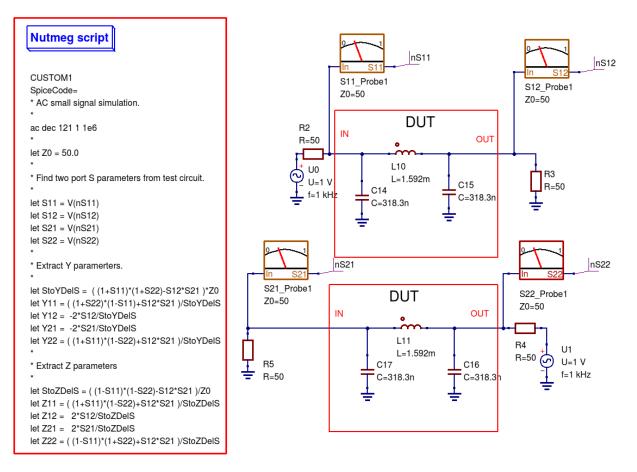

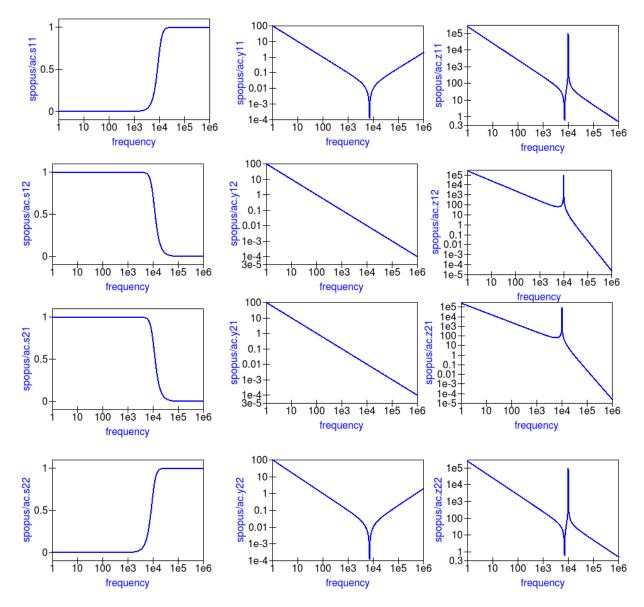

Figure 3.1 shows a Ques subcircuit model for a 15MHz centre frequency band pass passive filter. Note that the three distinct parts of a subcircuit model without parameters are: (1) a circuit representing the model body with one or more input (Pin) and output (Pout) pins plus connected components selected from Ques pre-defined components and user designed subcircuits ( there are no user defined subcircuits present in Figure 3.1), (2) a subcircuit symbol, and (3) a Ques netlist giving a list of the internal components, their connection nodes and a wrapper which defines the subcircuit. The syntax of the subcircuit netlist listed in Figure 3.1 is only understood by Ques and cannot be read without error by external SPICE simulators.

Figure 3.1 Ques 15MHz centre frequency band pass passive filter subcircuit without parameters

A test bench circuit for simulating the band pass filter circuit shown in Figure 3.1 is given in Figure 3.2. This figure includes a plot of the small signal AC output voltage for a filter with 50 Ohm input and output matching resistors. Note the use of a node voltage probe and the signal name allocated by Ques. Also note that the individual capacitor voltage and inductor current initial conditions are not set as they are not needed due to fact that the filter subcircuit is not DC biased. As a consequence the DC simulation icon shown in Figure 3.2 is not strictly necessary. However, its

a good idea to add it automatically to AC simulations because circuits with semiconductor devices or other non-linear components must have their small signal AC properties calculated, at their DC bias conditions, prior to small signal AC simulation.

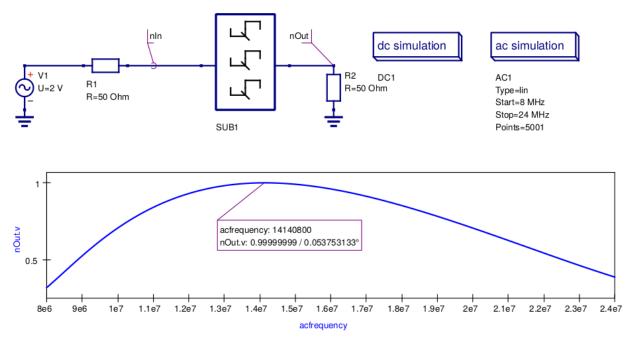

Figure 3.2 Ques 15MHz centre frequency band pass passive filter test bench with 50 Ohm source and load matching Figure 3.3 to Figure 3.5 present AC simulation results for the band pass filter generated with the Ngspice, Xyce and SPICEOPUS circuit simulators.

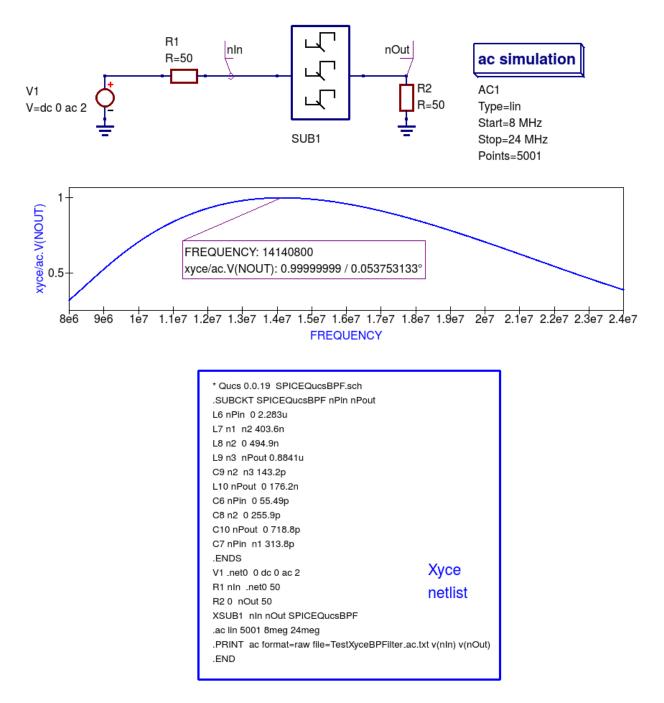

Figure 3.3 Band pass filter Ngspice test results and SPICE netlist for test bench circuit.

Figure 3.4 Band pass filter Xyce test results and SPICE netlist for test bench circuit.

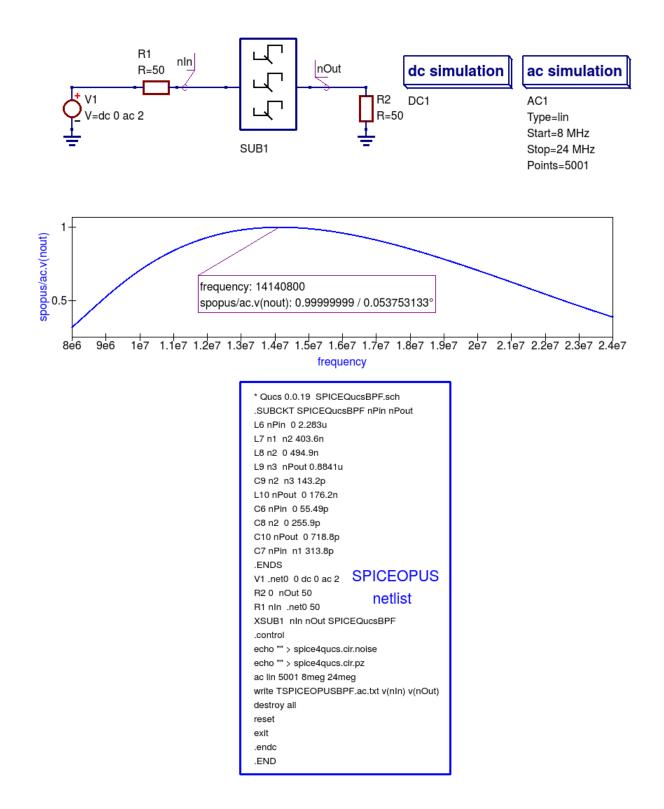

Figure 3.5 Band pass filter SPICEOPUS test results and SPICE netlist for test bench circuit.

Most readers will probably have noticed that the SPICE netlists for the Ngspice and SPICEOPUS band pass filter test benches are identical except for file names. This is because Ngspice and SPICEOPUS both include implementations of the SPICE 3f5 **Nutmeg** post simulation data processing package that is distributed with their SPICE engines.

These are not the same however, mainly because the SPICE OPUS development team have modified the original SPICE 3f5 Nutmeg package to firstly remove errors/bugs and secondly to improve its syntax. The extent to how this will affect the operation of spice4qucs is at this time unclear. If problems/bugs, due to implementation differences, surface in the future the spice4qucs Development Team will attempt to correct them as quickly as possible. The Xyce circuit simulator does not include a version of Nutmeg in its distribution package. This implies that Nutmeg style post simulation data processing is not possible with Xyce. However, to minimise the effects of this omission an extended form of the SPICE .PRINT statement has been implemented in Xyce, allowing algebraic expressions for data processing to be embedded in .PRINT statements. This topic and other aspects of Xyce post simulation data processing are covered in later sections of this help manual.

# 3.1.2 Spice4qucs subcircuits with parameters

Subcircuits which have component or physical parameter values set by a list of names and values attached to a schematic symbol add a significant "value added" feature to the subcircuit concept. This form of subcircuit can, for example, be used to represent manufacturers product variations which have identical circuits but require component values or device parameter values of differing value. Unfortunately, SPICE 3f5 only implements subcircuits without parameters. Recent generations of open-source GPL circuit simulators, including Ngspice, Xyce and SPICE OPUS, have been extended by their Development Teams to allow subcircuits with parameters. One consequence of this is that over time divergence of the SPICE subcircuit statement syntax has occurred amongst different circuit simulators. Spice4qucs implements a common subset of the published extended SPICE subcircuit syntax. This works well, but does have one disadvantage however, in that some published subcircuit netlists may require a small amount of editing before they will simulate with Spice4qucs. One code word often found in the SPICE extended subcircuit syntax is the term **PARAMS:**. This can occur in an **X** subcircuit call to signify a subcircuit with parameters. As this is optional in Ngspice, and indeed in other SPICE derived circuit simulators, it is not implemented in Spice4qucs.

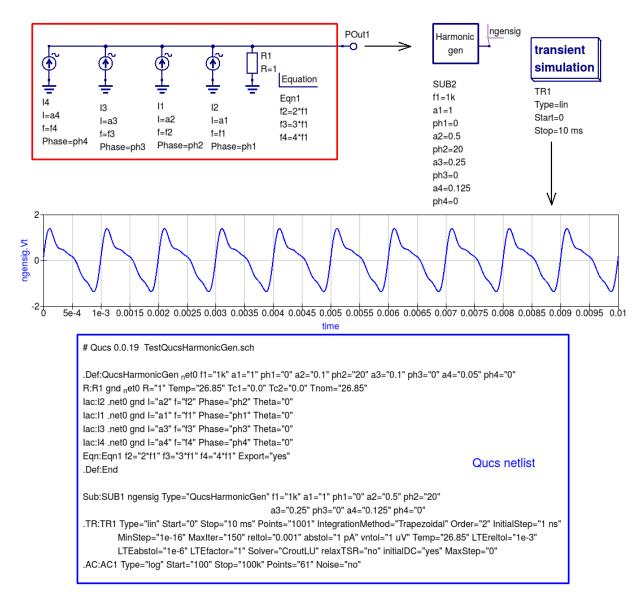

Quesator, Ngspice, Xyce and SPICEOPUS all allow parameters to be attached to subcircuit symbols and to be used in design equation calculations. As an introductory example Figure 3.6 illustrates a circuit schematic and user generated symbol for a simple Ques harmonic generator composed of a fundamental AC signal and three sinusoidal harmonic components. Parameters f1 to f4 set the frequencies of the harmonics. The Ques Equation block, at the subcircuit internal circuit level, is used to calculate the individual harmonic frequencies. In a similar fashion ph1 to ph4 represent the phases of the signal harmonics.

Figure 3.6 Ques subcircuit sinusoidal harmonic signal generator: f1 is the fundamental frequency and f2 to f4 the higher order harmonics; ph1 to ph4 the phases of the fundamental signal and its harmonics. For clarity long Ques netlist lines have been spread over more than one line.

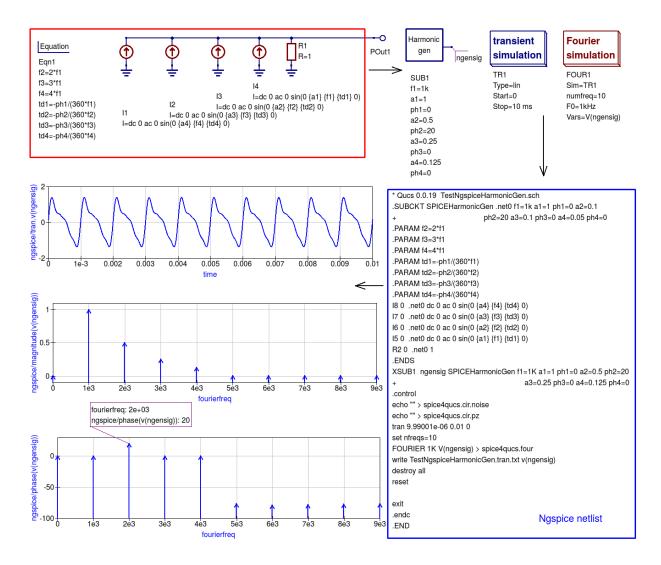

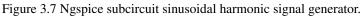

Figure 3.7 shows an Ngspice version of the Ques sinusoidal harmonic generator illustrated in Figure 3.6. A casual look at these two subcircuit diagrams shows that they are not dissimilar. However, there are a number of subtle changes apparent from the diagrams. First it is important to realise that the Ques and SPICE sinusoidal (sin) signal generator specifications are different; Oucs requires the signal phase and SPICE the signal delay to be specified as parameters. In Figure 3.7 extra equations to convert phase to time delay are added to Equation block Eqn1 inside subcircuit SPICEHarmonicGen. To ensure that Eqn1 variables, for example frequency  $f_2$ , are passed to the subcircuit component values as numerical values SPICE curly deliminator brackets, {...}, are placed round equation variable names. Finally, it is important to realize that the order of the variables in Equation blocks are important. Ques allows them to be in any order because it arranges all entries into a sequence which ensures each variable can be allocated a numerical value before it is used in other equations. However, SPICE does not do the same but assumes that all variables included in the right hand side of an equation have been allocated a numerical value prior to being used in the calculation of the variable named on the left hand side of the same equation. To check that the Ngspice generated waveform is correctly generated a Fourier analysis of signal V(ngensig) is displayed on Figure 3.7. At frequencies above f4 the phase values have no meaning. The simulated signal waveform obtained with SPICE OPUS was found to be similar to that obtained with NGSPICE, see Figue 3.8. Try simulating the sinusoidal harmonic generator waveform with SPICE OPUS to check this statement for your self.

Figure 3.8 Xyce subcircuit sinusoidal harmonic signal generator.

# 3.1.3 A second more complex example of Spice4qucs subcircuits with parameters

Variable assignment equations, defined in Ques *Equation Eqn* blocks and embedded in a subcircuit, are converted by Spice4ques into SPICE . PARAM statements. These are listed in the initial section of the SPICE-netlist of the circuit being simulated, or in the first section of a subcircuit netlist, allowing their values to be determined before the start of a simulation. With Ques *Equation Eqn* blocks it is important to remember that the variables defined cannot be functions of circuit voltage or current or any other voltage/current dependent properties. Restrictions placed by Spice4ques on the use of Ques *Equation Eqn* blocks are considered in detail in Chapter 4. However, one fundamental rule that must be followed at all times is that Ques simulation icons must not be placed inside a subcircuit.

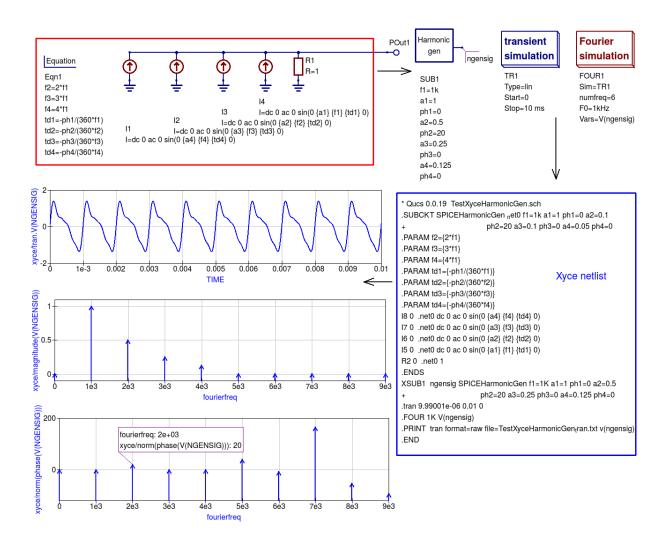

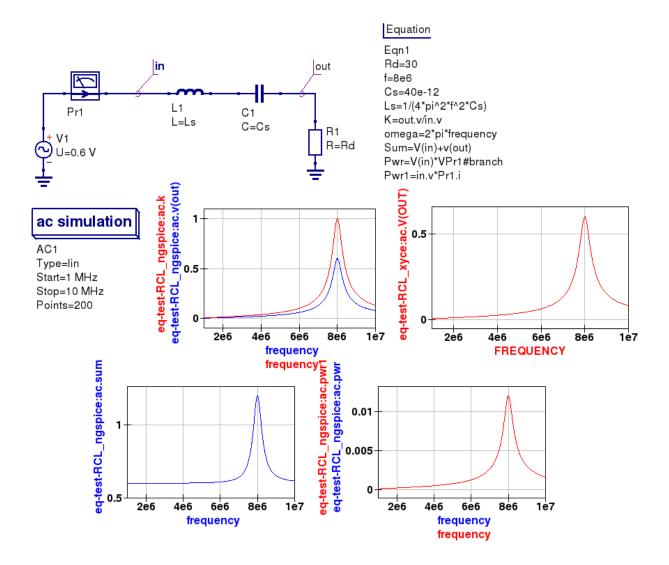

The electrical equivalent circuit of a HC-49/U 8.86 MHz Quartz crystal resonator is shown in Figure 3.9. In this model the crystal resonator is represented as the RCL parallel electric network illustrated in the following two schematics:

- quarz.sch Quartz crystal resonator subcircuit; Figure 3.9.

- quarz\_test.sch Spice4qucs test circuit; Figure 3.10.

These files can be found in the Qucs-S subdirectory examples \ngspice \.

Figure 3.9 shows the crystal resonator subcircuit. A brief introduction to the theory of crystal resonators can be found

at https://en.wikipedia.org/wiki/Crystal\_oscillator.

Figure 3.9 Equivalent circuit of Quartz crystal resonator.

In the HC-49/U Quartz crystal resonator model the RCL network has two resonant frequencies: a series resonance frequency f, where

$$f = \frac{1}{2\pi\sqrt{L_q C_q}}$$

and a parallel resonance frequency  $f_p$ , where

$$f_p = \frac{1}{2\pi\sqrt{L_qC_q}}\sqrt{1 + \frac{C_q}{C_s}}$$

Transposing equation f yields an expression for the series capacitance  $C_q$ , where

$$C_q = \frac{1}{4\pi^2 f^2 L_q^2}$$

This equation is placed in Ques Equation Eqn1 block inside the Quartz crystal resonator subcircuit.

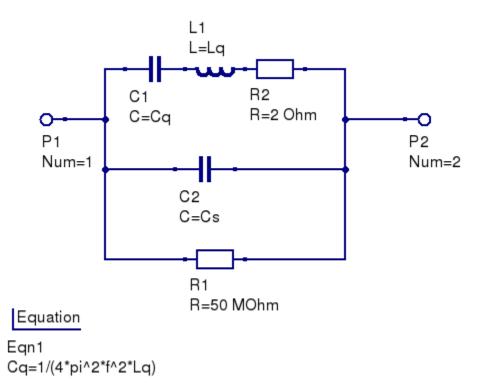

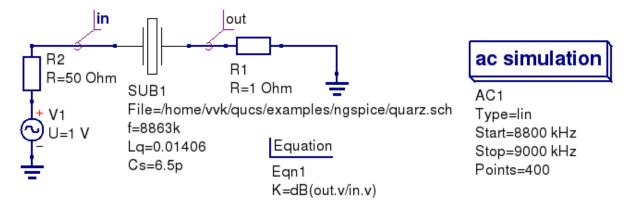

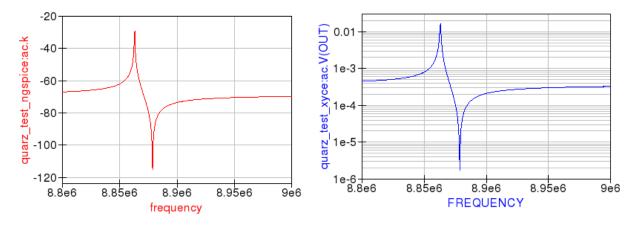

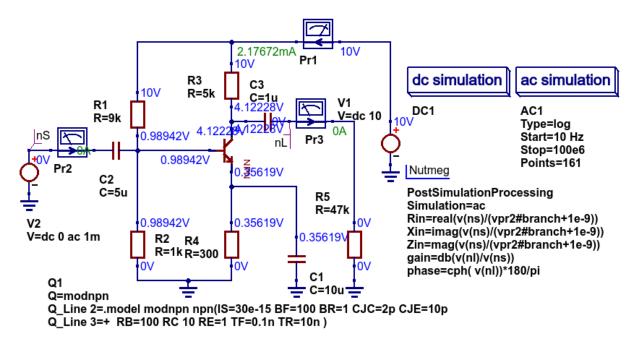

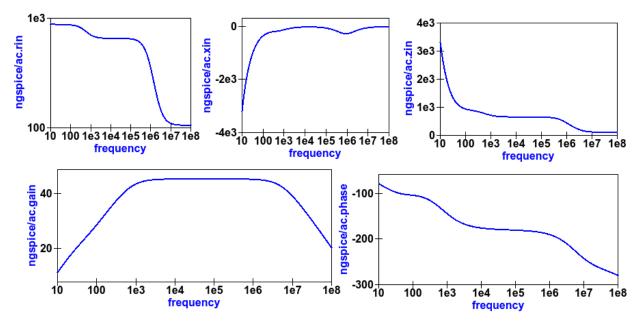

Performing an *AC simulation* with Ngspice and Xyce, using the test circuit given in Figure 3.10, yields the amplitude response data plotted in Figure 3.11, Ngspice transfer coefficient K(ac.k) and Xyce voltage ac.V(OUT).

Figure 3.10 Test circuit for Quartz crystal resonator.

Figure 3.11 indicates that the Ngspice and Xyce plotted results are identical. The only difference being that Xyce simulation result postprocessing is not implemented. Hence, only the Xyce output voltage can be plotted; this is done by choosing a logarithmic Y scale, then the Xyce plot effectively displays a scaled decibel output. The two resonant frequencies f and  $f_p$  are clearly visible on these plots.

Figure 3.11 Magnitude response of HC-49/U Quartz crystal.

Subcircuits are converted by Spice4ques into SPICE .SUBERT routines. The SPICE netlist for the Quartz crystal resonator test circuit, Figure 3.10, shown below illustrates how the Spice4ques handles SPICE .PARAM, . SUBCIRCUIT and subcircuit X call statements, placing them in the correct position within the SPICE netlist of the circuit being simulated.

```

* Oucs 0.0.19

/home/vvk/qucs/examples/ngspice/quarz_test.sch

1

/home/vvk/qucs/examples/ngspice/quarz.sch

* Qucs 0.0.19

2

.SUBCKT quarz _net0 _net1 f=8863k Lq=0.01406 \mbox{Cs=6.5p}

3

.PARAM Cq={1/(4*3.1415926539^2*f^2*Lq)}

4

R1 _net0 _net1 50MEG

5

C2 _net0 _net1

\{CS\}

6

R2 _net2 _net1

2

7

L1 _net3 _net2

\{LO\}

8

C1 _net0 _net3

\{CQ\}

9

.ENDS

10

R1 out 0 1

11

V1 _net0 0 DC 0 SIN(0 1 1G 0 0) AC 1

12

R2 _net0 in 50

13

in out quarz f=8863K Lq=0.01406 Cs=6.5P

XSUB1

14

```

```

.control

15

set filetype=ascii

16

AC LIN 400 8800K 9000K

17

let K=dB(V(out)/V(in))

18

write quarz_test_ac.txt v(in) v(out)

K

19

destroy all

20

exit

21

.endc

22

.END

23

```

### 3.2 Component and circuit libraries

Library components are supported in spice4qucs subsystem. You can use all library components. Some libraries have embedded original SPICE code of components. You should prefer to use these libraries to archive the best result with Spice simulation of Qucs schematics. The example of library component (IRFZ44 MOSFET from *MOSFETS* library) usage is examples/ngspice/irfz44\_switch.sch

### 3.3 Using manufacturers component data libraries

Electronic components manufacturers often provide spice models of components in datasheets. You can attach these datasheet spice models using *SPICE netlist* component. You need to perform the following steps to use Spice-model from component datasheet. Spice netlist builder substitutes SPICE-models directly to output netlist without any conversions.

1. Extract Spice netlist text and save it as text file. You can use any extension for this file. Preferable are .ckt , .cir, .sp

2. Place on schematic component *SPICE netlist* and attach SPICE netlist nodes to component port using standard *SPICE component properties* dialog.

3. Simulate schematic with Ngspice/Xyce.

It's need to note that SPICE-netlist of component **must not** be ended by .END directive. In this case simulator exits after it reads .SUBCKT routine and simulation cannot be executed.

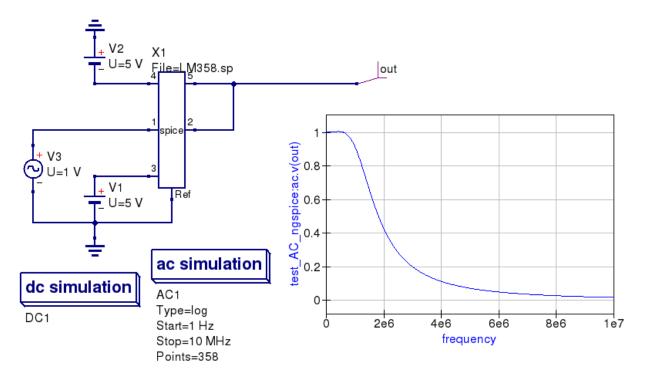

The example of spice model usage (LM358 opamp) is shown in the Figure 3.12

Figure 3.12 AC Simulation of LM358 opamp with Ngspice.

Here is the netlist of LM358 spice-model. Model can be found in LM358 datasheet.

```

* from http://www.ti.com/lit/zip/sloj045

* LM358 OPERATIONAL AMPLIFIER "MACROMODEL" SUBCIRCUIT

2

* CREATED USING PARTS RELEASE 4.01 ON 09/08/89 AT 10:54

3

* (REV N/A)

SUPPLY VOLTAGE: +/-5V

4

* CONNECTIONS:

NON-INVERTING INPUT

5

| INVERTING INPUT

6

*

| | POSITIVE POWER SUPPLY

7

*

| | | NEGATIVE POWER SUPPLY

8

*

| | | OUTPUT

9

*

10

*

.SUBCKT LM358

1 2 3 4 5

11

12

*

С1

11 12 5.544E-12

13

C2

6 7 20.00E-12

14

5 53 DX

DC

15

DE

54 5 DX

16

17

DLP 90 91 DX

DLN 92 90 DX

18

DP

4 3 DX

19

EGND 99 0 POLY(2) (3,0) (4,0) 0 .5 .5

20

7 99 POLY(5) VB VC VE VLP VLN 0 15.91E6 -20E6 20E6 20E6 -20E6

FΒ

21

6 0 11 12 125.7E-6

22

GΑ

0 6 10 99 7.067E-9

GCM

23

3 10 DC 10.04E-6

IEE

24

HLIM 90

0 VLIM 1K

25

Q1

11 2 13 QX

26

12 1 14 QX

Q2

27

6 9 100.0E3

28

R2

RC1

4 11 7.957E3

29

```

| 30 | RC2   | 4    | 12   | 7.957E3                  |

|----|-------|------|------|--------------------------|

| 31 | RE1   | 13   | 10   | 2.773E3                  |

| 32 | RE2   | 14   | 10   | 2.773E3                  |

| 33 | REE   | 10   | 99   | 19.92E6                  |

| 34 | RO1   | 8    | 5    | 50                       |

| 35 | RO2   | 7    | 99   | 50                       |

| 36 | RP    | 3    | 4    | 30.31E3                  |

| 37 | VB    | 9    | 0    | DC 0                     |

| 38 | VC 3  | 53   | DC   | 2.100                    |

| 39 | VE    | 54   | 4    | DC .6                    |

| 40 | VLIM  | 7    | 8    | DC 0                     |

| 41 | VLP   | 91   | 0    | DC 40                    |

| 42 | VLN   | 0    | 92   | DC 40                    |

| 43 | .MODE | EL I | DX I | D(IS=800.0E-18)          |

| 44 | .MODE | EL Ç | QX I | PNP(IS=800.0E-18 BF=250) |

| 45 | .ENDS | 5    |      |                          |

| 46 |       |      |      |                          |

#### 3.4 Usage of unmodified SPICE Libraries

#### 3.4.1 SpiceLibComp device

You can use an unmodified SPICE libraries with new SpiceLibComp device. This component could be found at the *File components* group. This component have three properties:

- File is full SPICE library file (usually \*.lib, \*.cir, or \*.sp files) path. You can use unmodified library here.

- Device is SUBCKT entry name that represents desired device. Every component is defined as subcircuit and identified by . SUBCKT entry name. This property holds device name. You need to fill this property manually.

- SymPattern is symbol pattern for device. You can select one of predefined symbol patterns or use automatic pattern. Automatic pattern is simple rectangular symbol with pins.

Let's consider SPICE library structure. There exists a SPICE library file ad822.cir that contains AD822 model. Here is library source code:

```

.SUBCKT AD822 1 2 99 50 25

1

*

2

\star INPUT STAGE & POLE AT 5 MHz

3

R3 5 99 2456

4

R4 6 99 2456

5

CIN 1 2 5E-12

6

C2 5 6 6.48E-12

7

I1 4 50 108E-6

8

IOS 1 2 1E-12

9

EOS 7 1 POLY(1) (12,98) 100E-6 1

10

J1 5 2 4 JX

11

J2 6 7 4 JX

12

GB1 50 2 POLY(3) (2,4) (2,5) (2,50) 0 1E-12 1E-12 1E-12

13

GB2 50 7 POLY(3) (7,4) (7,5) (7,50) 0 1E-12 1E-12 1E-12

14

15

* GAIN STAGE & POLE AT 13.4 HZ

16

EREF 98 0 (30,0) 1

17

R5 9 98 2.313E6

18

C3 9 25 32E-12

19

G1 98 9 (6,5) 4.07E-4

20

```

```

V1 8 98 0

21

V2 98 10 -1

22

D1 9 10 DX

23

D2 8 9 DX

24

25

* COMMON-MODE GAIN NETWORK WITH ZERO AT 1 KHZ

26

R21 11 12 1E6

27

R22 12 98 100

28

C14 11 12 159E-12

29

E13 11 98 POLY(2) (2,98) (1,98) 0 0.5 0.5

30

31

* POLE AT 10 MHZ

32

R23 18 98 1E6

33

C15 18 98 15.9E-15

34

G15 98 18 (9,98) 1E-6

35

36

*

* OUTPUT STAGE

37

ES 26 51 POLY(1) (18,98) 1.72 1

38

RS 26 22 500

39

V3 23 51 1.03951

40

V4 21 23 1.36

41

C16 20 25 2E-12

42

C17 24 25 2E-12

43

RG1 20 97 1E8

44

RG2 24 97 1E8

45

Q1 20 20 97 PNP

46

Q2 20 21 22 NPN

47

Q3 24 23 22 PNP

48

Q4 24 24 51 NPN

49

Q5 25 20 97 PNP 20

50

Q6 25 24 51 NPN 20

51

VP 96 97 0

52

VN 51 52 0

53

EP 96 0 POLY(1) (99,0) 0.01 1

54

EN 52 0 POLY(1) (50,0) -0.015 1

55

R25 30 99 63.5E3

56

R26 30 50 63.5E3

57

FSY1 99 0 VP 1

58

FSY2 0 50 VN 1

59

60

* MODELS USED

61

62

.MODEL JX NJF (BETA=7.67E-4 VTO=-2.000 IS=1E-12)

63

.MODEL NPN NPN(BF=120 VAF=150 VAR=15 RB=2E3 RE=4 RC=200)

64

.MODEL PNP PNP(BF=120 VAF=150 VAR=15 RB=2E3 RE=4 RC=900)

65

.MODEL DX D(IS=1E-15)

66

.ENDS AD822

67

```

This library example contains only one model defined by one subcircuit entry, but you can use any library containing any amount of device models.

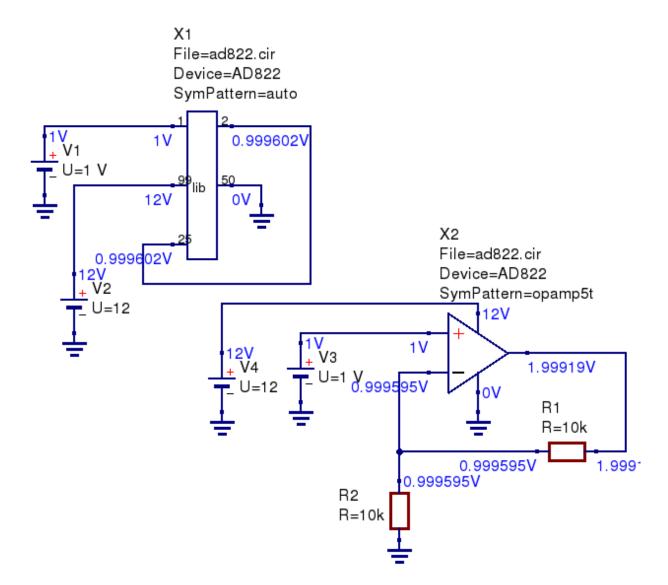

Let's use AD822 opamp model. Create new schematic and place SpiceLibComp device on schematic (Figure 3.13). Select ad822.cir file in the first property. Then fill ad822 (device name) in the second property.

You can either create an automatic component symbol, either use one of the predefined patterns. At current state only opamp3t and opamp5t patterns are available. These patterns represents three- and five-terminal opamps respectively. Symbol patterns are Ques XML files. They are placed in the share/ques/symbols subdirectory of the Ques installation root. These files have \*.sym extension. Symbol pattern format will be considered further.

SPICE netlist builder performs automatic port assignment for subcircuit pins. If automatic symbol is used symbol pin names will be automatically filled from the .SUBCKT entry definition. See Figure 3.13 for example of the automatic pin assignment.

If symbol pattern is used, the first .SUBCKT entry port will be automatically mapped to the first symbol port, etc. Symbol port sequence is defined in the symbol pattern file (\*.sym) in Port description lines.

Figure 3.13 LM358 opamp library model usage with SpiceLibComp device

#### 3.4.2 Symbol pattern files format description

Let's consider symbol files format. Symbols have \*.sym extension and are placed in share/qucs/symbols subdirectory of the Qucs installation tree. Qucs automatically scans content of this subdirectory and displays all found valid symbols in drop-down list in the third property (SymPattern) of the *SpiceLibComp* device. User can select any symbol for new SPICE library device. It's need to create a new symbol file and place it into symbols directory to add new symbols to the existing Qucs installation.

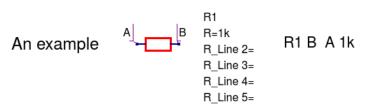

Let's consider symbol file format. Symbols have Ques XML schematic format without header. An example of symbol

file (five-terminal opamp) is shown in the listing below:

```

<Symbol>

1

<Line -20 -40 0 80 #000080 2 1>

2

<Line -20 -40 60 40 #000080 2 1>

3

<Line -20 40 60 -40 #000080 2 1>

4

<Line 40 0 20 0 #000080 2 1>

5

<Line -40 -20 20 0 #000080 2 1>

6

<Line -40 20 20 0 #000080 2 1>

7

<Line -15 20 10 0 #000000 2 1>

8

<Line -10 -25 0 10 #ff0000 0 1>

9

10

<Line -15 -20 10 0 #ff0000 0 1>

<Line 10 -20 0 -20 #000080 2 1>

11

<Line 10 20 0 20 #000080 2 1>

12

<.PortSym 10 40 4 0>

13

<.PortSym 10 -40 3 0>

14

<.PortSym -40 20 2 0>

15

<.PortSym -40 -20 1 0>

16

<.PortSym 60 0 5 180>

17

<.ID 30 24 OP>

18

</Symbol>

19

```

Automatic symbol files preparation is not yet implemented, but you can use Ques schematic editor to create new symbol files. You may use the following sequence to create new symbol:

- Create Ques subcircuit. Subcircuit may be empty. Place desired ports on it;

- Attach symbol to it using switching to symbol mode by F9 keystroke. Wire subcircuit ports to symbol and paint symbol outline.

- Save subcircuit, open it with any test editor and copy-paste symbol code form it into the symbol file.

Please pay attention to the proper port mapping. Let's consider port definition line format:

<.PortSym 10 -40 3 0>

This port definition consists of five space separated fields. The fourth field (3) contains port number. This port number should match SPICE . SUBCKT port number (not port name!) to proper component wiring. You may need to edit this field manually.

For example AD822 has the following definition in our library:

.SUBCKT AD822 1 2 99 50 25

Subcircuit node list follows after the subcircuit name (AD822). Subcircuit nodes will be mapped to component port in the following sequence:

- Node 1 to Port 1

- Node 2 to Port 2

- Node 99 to Port 3

- Node 50 to Port 4

- Node 25 to Port 5

#### 3.5 Usage of the whole SPICE library

Ques-S supports usage of the whole SPICE libraries. Such libraries will be visible in the **QuesLib** tool and left-side **Library** dock. Library modification will be not required, but user may need to attach components symbols as resource

files.

Let's consider how to use it. SPICE library again will be treated as a set of .SUBCKT entries. You should give \*.lib extension an existing SPICE library and put in into \$HOME/.qucs/user\_lib or system Qucs library directory (for example /usr/share/qucs-s/library for Unix). Then you can get access to this newly added SPICE library via QucsLib tool or from the left-side dock. You will see its name and component list (Figure 3.14).

| 🔊 👩 Ques Library Tool 0.0.19               |                                                 |

|--------------------------------------------|-------------------------------------------------|

| <u>F</u> ile <u>H</u> elp                  |                                                 |

| Component Selection                        | Component                                       |

| <ul> <li>ad822 ✓</li> <li>AD822</li> </ul> | Name: AD822<br>Library: ad822                   |

|                                            | AD822 device from ad822 library                 |