# **OpenPET**

# **OpenPET User's Guide Documentation** Release 2.2

**OpenPET**

October 28, 2016

| 1 | Abbreviations                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                               |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 2 | OpenPET v2.3 Release Notes         2.1       What's New         2.2       Upgrading from Previous Releases of OpenPET                                                                                                                                                                                                                                                                            | <b>3</b><br>3<br>4                                              |

| 3 |                                                                                                                                                                                                                                                                                                                                                                                                  | 5<br>9<br>13<br>14                                              |

| 4 | 4.1Getting Hardware4.2Assembling the Hardware4.3Downloading the Software and Firmware4.4Small System: Programming OpenPET Flash Images4.5Standard System: Programming OpenPET Flash Images4.6Running OpenPET System4.7Example System Setup & Data Acquisition of a Small System in Oscilloscope Mode4.8Example System Setup & Data Acquisition of a Small System in Singles Mode4.9Data Analysis | <b>17</b><br>17<br>20<br>32<br>36<br>37<br>39<br>41<br>41<br>51 |

| 5 | 5.1 Bus IO                                                                                                                                                                                                                                                                                                                                                                                       | <b>53</b><br>54<br>54                                           |

| 6 | <ul> <li>6.1 Support Board with Detection Firmware</li> <li>6.2 Support Board with Coincidence Firmware</li> </ul>                                                                                                                                                                                                                                                                               | <b>61</b><br>61<br>64<br>64                                     |

| 7 |                                                                                                                                                                                                                                                                                                                                                                                                  | <b>67</b><br>73                                                 |

| 8 | 8.1 Installing ROOT                                                                                                                                                                                                                                                                                                                                                                              | <b>89</b><br>89<br>89                                           |

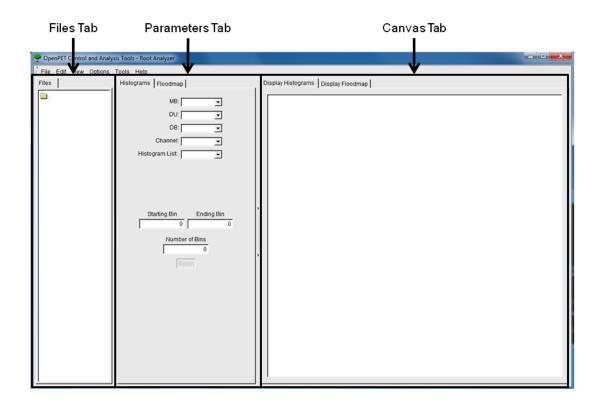

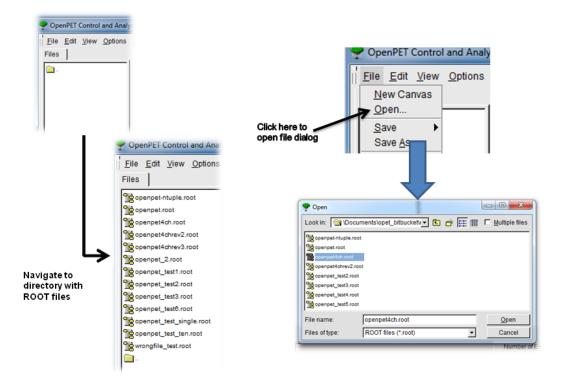

|    | 8.3          | OpenPET CAT Graphic User Interface                                                        | 93         |

|----|--------------|-------------------------------------------------------------------------------------------|------------|

| 9  | Ackn         | owledgements                                                                              | 113        |

| 10 | 10.1         | ndices         Appendix 1: Default Values         Appendix 2: Troubleshooting Diagnostics |            |

| 11 | 11.2<br>11.3 | ta<br>Firmware                                                                            | 121<br>121 |

| 12 | Index        |                                                                                           | 123        |

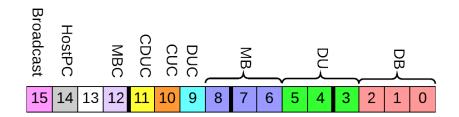

# Abbreviations

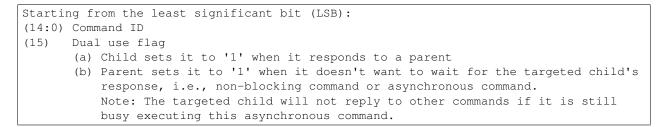

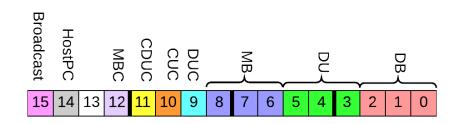

CDUC: Coincidence Detector Unit Controller CI: Coincidence Interface Board C/R: Commands and Responses CU: Coincidence Unit CUC: Coincidence Unit Controller DB: Detector Board **DST:** Destination DU: Detector Unit DUC: Detector Unit Controller EPCS: Enhanced Programming Configuration Serial device FIFO: First-in, First-out Data Buffer FPGA: Field-Programmable Gate Array MB: Multiplexer Board MBC: Multiplexer Board Controller PLL: Phase-Locked Loop SB: Support Board SRC: Source TDC: Time-to-Digital Converter

# **OpenPET v2.3 Release Notes**

# 2.1 What's New

#### 2.1.1 Firmware

- Add standard system support.

- New commands to read the node type and version.

- Firmware and software version are embedded at compile time and based on repo tag.

- Build scripts are more generic and cross platform.

- Many bug fixes. See repository changelog.

#### **SupportBoard**

- Add standard system support.

- Improve Singles real-time data handling (synchronization, random selection, and output overflow).

- Improve multi crate synchronization.

- Improve QuickUSB timing to reduce number of errors.

#### **DetectorBoard**

- Add standard system support.

- Add new singles mode to compute energy for the first four channels.

- Add baseline removal core.

- Improve multi crate synchronization.

- Multiphase TDC uses correct output stage clock.

#### 2.1.2 Embedded Software

- Add standard system support.

- New commands to read the node type and version.

• Expand SPI interface to handle CUC and DUC intercommunication.

#### **SupportBoard**

#### Main FPGA

• No changes.

#### **IO FPGAs**

• No changes.

#### **DetectorBoard**

• No changes.

#### 2.1.3 Software

- Add standard system support.

- New Scripts to handle and plot Singles example.

- New script to validate scope mode data integrity for large files 10GB+.

#### 2.1.4 Hardware

• No changes.

# 2.2 Upgrading from Previous Releases of OpenPET

• Standard system changes are not backward compatible.

# **System Overview**

This document describes the OpenPET electronics system. The purpose of the OpenPET electronics is to provide a system that can be used by a large variety of users, primarily people who are developing prototype nuclear medical imaging systems. These electronics must be extremely flexible, as the type of detector, camera geometry, definition of event words, and algorithm for creating the event word given the detector outputs will vary from camera to camera. This implies that users must be able to modify the electronics easily, which further implies that they have easy access to documentation, including the schematics and documents needed to fabricate the circuit boards (Gerber files, bill of materials, etc.) and source code (for both firmware and software). They also need support in the form of instructions, user manuals, and a knowledge base, and they want fabricated circuit boards to be readily available.

Thus, the OpenPET electronics system includes hardware, firmware, and software. It is scalable enough to provide solutions ranging from a "test bench" for a small number of detector modules to a complete camera. It is also "open source" to both maximize flexibility and minimize redundant development.

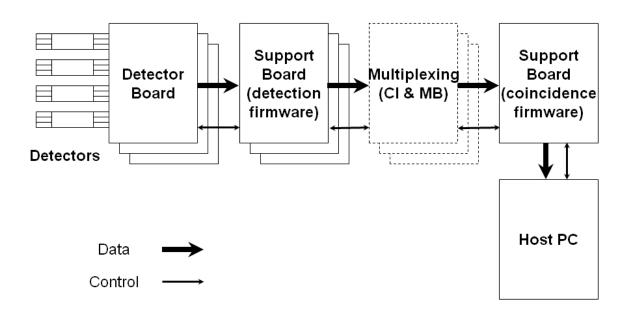

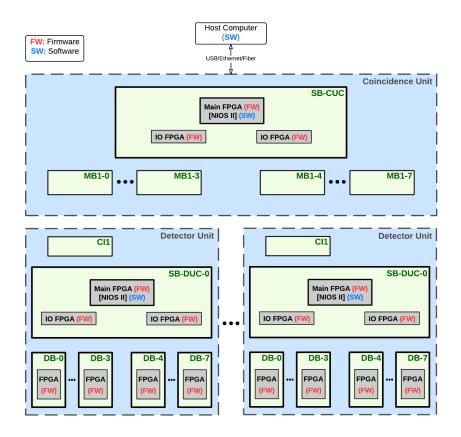

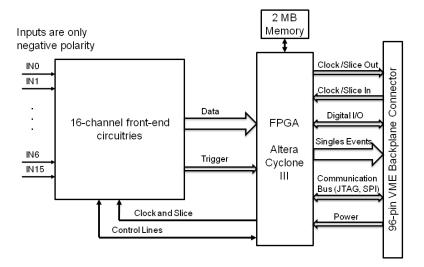

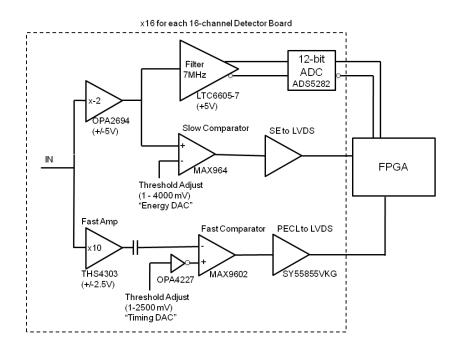

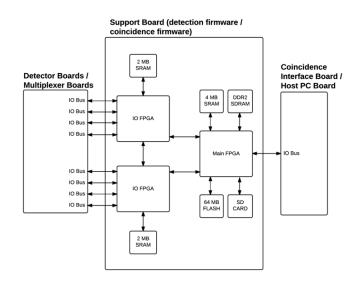

The basic system architecture is shown in Fig. 3.1. There are four types of custom electronics boards in the system: the Detector Board (DB), the Support Board (SB), the Coincidence Interface Board (CI), and the Multiplexer Board (MB). The Support Board plays two roles in the system, depending on the firmware.

The general data flow is that analog signals from detector modules provide the inputs to the Detector Board. This board processes the analog signals to create a singles event word, which is a digital representation of this single gamma ray interaction. The singles event words are passed to the Support Board loaded with detection firmware, whose main function here is to multiplex the singles event words from multiple Detector Boards. The singles event words are then passed through the Coincidence Interface Board to the Multiplexer Board, which can provide a further layer of multiplexing for singles event words, if necessary. Next the multiplexed singles event words are passed to another Support Board loaded with coincidence firmware, which searches through the singles event words for pairs that are in time coincidence and then forms coincidence event words. These coincidence event words are then passed to the Host PC. Optionally, the Support Board with coincidence firmware can act as a multiplexer and pass unaltered singles event words to the Host PC.

# 3.1 Definitions

The OpenPET components are housed in an assembly whose form factor is the same as a 12-slot VME crate that accommodates 6U boards. A Support Board essentially replaces the backplane of the VME crate and all the other boards plug into it. The plug-in boards have the same form factor as a VME 6U board, except that the position of the connectors is offset (compared to true VME boards) to prevent OpenPET boards from being plugged into standard VME systems and vice versa.

Fig. 3.1: Schematic of the OpenPET system architecture.

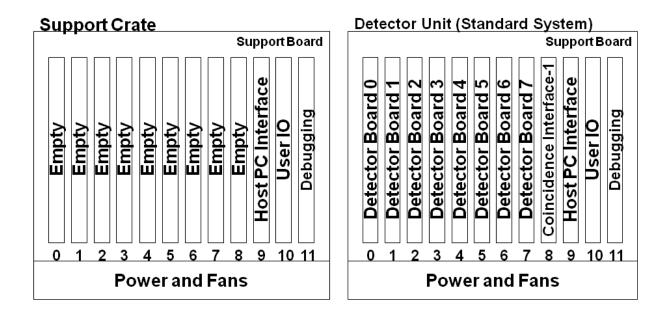

# 3.1.1 Support Crate

A Support Crate (Fig. 3.2) is conceptually similar to a VME crate (with controller), namely an intelligent support structure that "functional" boards can be plugged into. It consists of a mechanical frame with 12 plug-in slots, a Support Board (that has a considerable amount of programmable processing power and also acts as a backplane), power supplies, cooling fans, and appropriate boards plugged into slots 9-11. Slots 0-8 are vacant. Slot 9 holds a Host PC Interface Board, which is used to communicate with the Host PC; this board is optional. Slot 10 holds a User IO Board, which allows users to interface to external components such as EKG signals and motor controllers; this board is optional. Slot 11 holds a Debugging Board, which has interfaces to logic analyzers, a number of diagnostic LEDs, an external clock input, and a JTAG connector; this board is optional. Some ancillary components (such as DRAM memory and a QuickUSB board) are also necessary for a functioning Support Crate. By programming the Support Board with appropriate (but different) firmware, the Support Crate becomes part of either a Detector Unit or a Coincidence Unit.

#### 3.1.2 Detector Unit

A Detector Unit (DU), as shown in Fig. 3.2 consists of a Support Crate with between one and eight Detector Boards plugged into slots 0-7. Each Detector Board can process up to 16 or 32 analog input signals. A Detector Unit can therefore process up to 128 or 256 analog signals, which corresponds to 32 or 64 conventional block detector modules (with 4 analog outputs per module). In a Small System (Fig. 3.4), Slot 8 is empty (if data is transferred to the Host PC through USB or Ethernet via the Host PC Interface Board plugged into Slot 9). In a Standard (Fig. 3.5) or Large System (Fig. 3.6), a Coincidence Interface Board must be plugged into Slot 8 of the Detector Unit. There are two versions of the Coincidence Interface Board: Coincidence Interface Board-1 (CI-1) for the Standard System and Coincidence Interface Board-8 (CI-8) for the Large System. At present, the Coincidence Interface Board-8 has not been designed or specified. These boards transfer event data and bidirectional control data between the Detector Unit and a Coincidence Unit.

In a Small System (see *Small System* (page 10)), the Support Board in the Detector Unit is programmed to multiplex outputs from the Detector Boards, process coincident events, and pass the coincident events to the Host PC. It can also be programmed to multiplex singles events and pass them to the Host PC. In a Standard or Large System (see *Standard System* (page 10) and *Large System* (page 12)), the Support Board in the Detector Unit is programmed to multiplex singles events from the Detector Boards and forward them to a Coincidence Unit.

### 3.1.3 Coincidence Unit

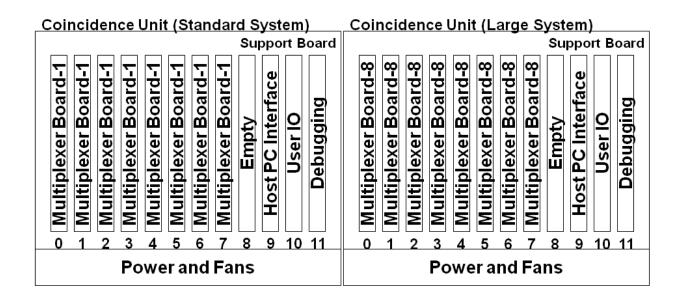

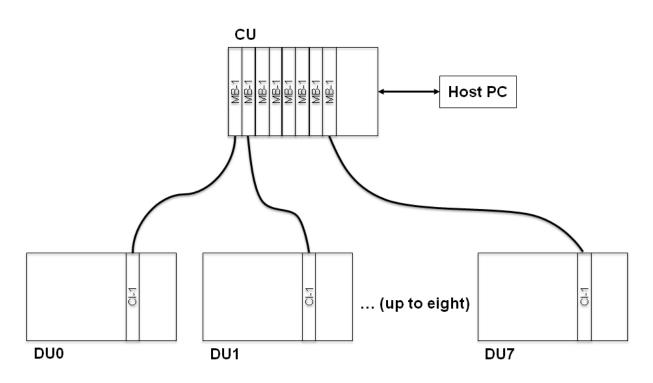

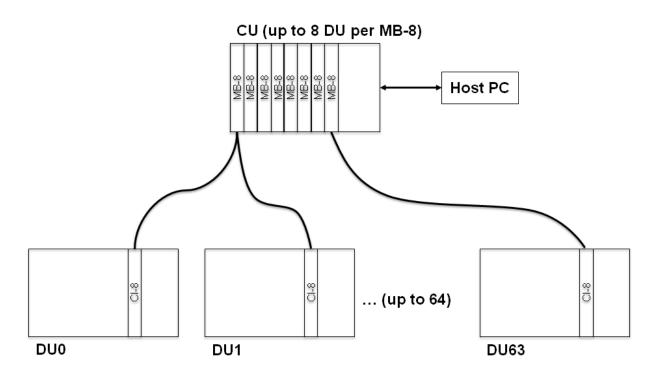

In Small Systems, the coincidence processing is performed on the Detector Unit's Support Board. In Standard and Large Systems, the coincidence processing is performed in a Coincidence Unit (CU) as shown in Fig. 3.3.

The Coincidence Unit for a Standard System consists of a Support Crate with between one and eight Multiplexer Boards plugged into slots 0-7. The Support Board is loaded with firmware to perform the coincidence processing. Each Multiplexer Board communicates with one Detector Unit via the Coincidence Interface Board using a cable. Similar to the Coincidence Interface Board, there are two versions of the Multiplexer Board: Multiplexer Board-1 (MB-1) for the Standard System and Multiplexer Board-8 (MB-8) for the Large System. At present, the Multiplexer Board-8 has not been designed or specified. The Coincidence Unit's Support Board is programmed to do the coincidence processing and pass the coincident events to the Host PC, although it can also function as a multiplexer and forward singles events. Data is transferred to the Host PC either through USB or Ethernet via the Host PC Interface Board plugged into Slot 9.

In a Coincidence Unit, the Support Board that acts as a backplane for the Support Crate is loaded with coincidence firmware. In this case, the Support Board with related firmware and software is called a **Coincidence Unit Controller** (CUC).

In the Coincidence Unit for the Standard System, each MB-1 connects with only one Detector Unit via a single cable, allowing up to 64 Detector Boards (or 512 block detector modules) in the system. In the Coincidence Unit for a Large

Fig. 3.2: Support Crate (left) and Detector Unit (right). A Detector Unit is a Support Crate with up to 8 Detector Boards (in Slots 0-7). For a Small System, Slot 8 is usually empty, although a Coincidence Interface Board can (optionally) be plugged into it. For Standard and Large Systems, a Coincidence Interface Board must be plugged into Slot 8.

System, the MB-8s plugged into slots 0-7 connect via cables (one cable per Detector Unit) with up to 8 Detector Units, allowing up to 512 Detector Boards (or 4096 block detector modules) in the system. The MB-8s are programmed to serve as multiplexers for events coming from up to 8 Detector Units. Due to the nature of multiplexing, this allows a larger number of channels to be serviced, but does not increase the maximum total event rate (singles or coincidence).

Fig. 3.3: Coincidence Unit for a Standard System (left) and a Large System (right). For both Standard and Large Systems, a Coincidence Unit is a Support Crate with up to 8 Multiplexer Boards (in slots 0-7). In a Large System, the Multiplexer Boards function as multiplexers.

# 3.2 System Configuration

OpenPET can be configured either as a Small System, Standard System, or Large System, with the difference primarily due to the number of analog signals that can be read out. To determine which system components you need, the first step is to determine how many DBs are necessary. Each DB can process up to 16 or 32 analog signals (depending on the DB used, mixing of different types of DB is not supported), so the minimum number of DBs necessary is the number of analog signals divided by 16 or 32. While information can be shared between DBs, processing is far easier if all the signals from the same detector module are on the same DB. Thus, if your detector module has 5 analog outputs and you use a 16-channel DB, it is easiest to have each DB process 15 analog signals (i.e., from three detector modules) and not use the extra channels on each Detector Board. Thus, the initial estimate for the number of DBs necess. This

estimate may be modified due to the camera topology, as described in the following subsections. Once you have determined this initial estimate for the number of Detector Boards, you can determine whether you will need a Small, Standard, or Large OpenPET System.

#### 3.2.1 Small System

If the total number of Detector Boards is 8 or fewer, you can use a Small System (Fig. 3.4). This consists of a single Detector Unit (defined in *Detector Unit* (page 7)) connected to a Host PC. A Detector Unit (DU) can have anywhere between 1 and 8 DBs plugged into it. The initial estimate of the number of DBs in your system may need to be increased to support the camera topology. In the Small System, the default coincidence processing algorithm searches for coincidences between singles events that originate on different DBs, but it doesn't allow coincidences between singles on the same DB. Thus, more DBs may be necessary to allow all the desired coincidences, as none of the modules in a DB can be in coincidence with each other.

As an example, consider a four-headed PET system, where each head consists of a 2x2 array of detector modules and each detector module has five analog outputs. The OpenPET system would be configured as follows. Each 16-channel DB would service 3 detector modules, using 15 analog channels and leaving one channels on each DB unused. As the system consists of 16 detector modules (four heads of four modules each), the initial estimate for the number of DBs is six. To see whether the appropriate coincidences can be accommodated, we first try to distribute the detector modules as follows. DB 0 services three modules from head 0, DB 1 services one modules from head 0 and two from head 1, DB 2 services two modules from head 3, and DB 5 services one modules from head 3. Unfortunately, this will not work, as two Detector Boards (numbers 1 and 2) service modules from two different heads, which means that the system will not look for all possible coincidences between detector modules that are in different heads. No amount of redistributing the modules among the DBs will satisfy these criteria either. Thus, the only way the coincidence criteria can be satisfied (using the default coincidence processing software) is to use two DBs per head, for a total of eight Detector Boards. While the coincidence processing software can be rewritten to allow coincidences between two singles events that originate in the same DB, this is likely to make the firmware more complex and take significantly longer and cost more than purchasing two additional Detector Boards.

Fig. 3.4: Configuration of a Small OpenPET System.

#### 3.2.2 Standard System

If the total number of DBs is between 9 and 64, you can use a Standard System (Fig. 3.5). This consists of between 2 and 8 DUs (defined in *Detector Unit* (page 7)) and a single CU (defined in *Coincidence Unit* (page 7)) connected

to a Host PC. The DUs are connected to the CU via the Coincidence Interface Board CI-1 in each of the DUs and the Multiplexer Board MB-1 in the CU. Determining the number of DUs and DBs per DU needed follows the same principles as described in the Small System section. Each DU should only contain modules that will not be in coincidence with each other, as the default coincidence processing software does not allow coincidences between detectors that originate from the same DU. The DU should then contain the minimum number of DBs necessary to service all the required detector modules.

Each DU services a maximum of eight DBs, and each 16-channel DB services a maximum of 16 analog inputs (note that a conventional PET block detector has four analog outputs, one for each photomultiplier tube). Thus, the Standard System can support a maximum of 1,024 analog inputs (16 analog channels per DB, 8 DBs per DU, and 8 DUs per CU), which corresponds to 256 block detector modules.

As an example, consider a cylindrical PET camera, where each detector module has four analog outputs and covers a 5 cm x 5 cm area. There are 44 detector modules per ring (roughly 70 cm diameter) and 5 rings (25 cm axial coverage). The OpenPET system would be configured as follows. The system consists of 220 detector modules. Each 16-channel DB would service 4 detector modules. As there are a maximum of eight DBs per DU, a DU can service a maximum of 32 of these detector modules. If we divide the 220 modules by 32 modules per DU, we find that the system requires 6.875 DUs. Since DUs are quantized, it really needs 7 DUs, with each DU servicing 32 detector modules. In order to make sure that the correct coincident pairs will be collected, the modules in each DU should be selected so that each DU services a "pie slice" that spans  $\sim$ 51° azimuthally and the full 25 cm axial thickness.

# **OpenPET Standard System**

Fig. 3.5: Configuration of a Standard OpenPET System. Each of slots 0-7 in the Coincidence Unit contains a Multiplexer Board-1 that services a single DU. Slot 8 in the Detector Unit contains a Coincidence Interface Board-1 that transfers event data and bidirectional control between the DU and CU.

# 3.2.3 Large System

If the total number of DBs is between 65 and 512, you must use a Large System (Fig. 3.6). This consists of between 9 and 64 DUs (defined in *Detector Unit* (page 7)) and a single CU (defined in *Coincidence Unit* (page 7)) connected to a Host PC. The DUs are connected to the CU via the CI-8 in each of the DUs and the MB-8 in the CU. Determining the number of DUs and DBs per DU needed follows the same principles as described in the Standard System section. The difference between the Standard and Large Systems is that the Multiplexer Board-8 that plugs into slots 0-7 of the CU contains active circuitries (i.e., FPGA, etc.) that are configured as multiplexers. This allows each of the eight slots in the CU to service up to eight DUs (in a Standard System, each CU slot services a single DU). Thus, the Large System can support a maximum of 8,192 analog inputs (16 analog channels per DB, 8 DBs per DU, and 64 DUs per CU), which corresponds to 2,048 block detector modules. Again, the group of DUs processed by one slot in the CU should only contain modules that will not be in coincidence with each other, as the default coincidence processing software does not allow coincidences between detectors serviced by the same CU slot. The DU should then contain the minimum number of DBs necessary to service all the required detector modules.

# **OpenPET Large System**

Fig. 3.6: Configuration of a Large OpenPET System. Each of slots 0-7 in the CU contains a Multiplexer Board-8 that operates as a multiplexer, allowing that slot to service between 1 and 8 DUs. Slot 8 in the Detector Unit contains a Coincidence Interface Board-8 that transfers event data and bidirectional control between the DU and CU.

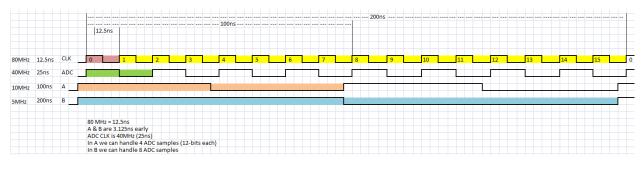

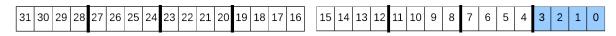

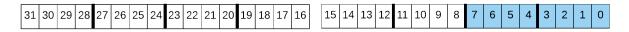

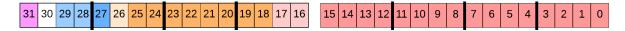

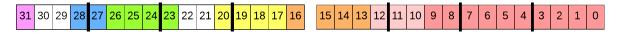

# 3.3 Timing & Timing Signals

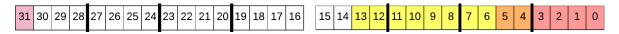

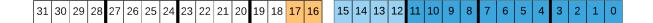

The system level timing signals are shown in Fig. 3.7. There are two timing signals-the system clock, which is an 80 MHz clock signal, and the time slice boundary, which defines the beginning of a time slice. The firmware will support both "short" and "long" event words. In "short" mode, the time slice boundary is generated every eight system clock cycles, while in "long" mode it is generated every sixteen system clock cycles. The choice creates a tradeoff-in "short" mode the dead time is a factor of two shorter, but the number of bits per event word is also a factor of two smaller.

The general concept is that the system divides time into small, fixed length time slices (100-200 ns or 8-16 clocks). All individual operations must occur within a single time slice, which implies that only singles event words that occur in the same time slice can be combined to form a coincident event. Since it can take significantly longer than a single time slice to fully process a single event, the system is pipelined so that the processing is divided into smaller steps that each can be completed in a single time slice.

During one time slice, each of the boards in a Standard System that output singles event words (i.e., DB, CI-1, and MB-1) can pass four singles event words. Thus, the maximum singles rate seen at the CI-1 output of each Detector Unit is 4 singles event words per time slice, or approximately 40 million "short" singles event words per second. Thus, 32 singles event words (four for each of the eight CI-1) enter the Coincidence Unit per time slice, or approximately 320 million "short" singles event words per second. In a Standard System, there are 8 Detector Units with 28 possible Detector Unit - Detector Unit combinations. So theoretically the Coincidence Unit can identify 448 coincident events per time slice (16 for each of the 28 Detector Unit-Detector Unit combinations), corresponding to 4.48 billion coincidence event words per second. In practice, the maximum event rate is limited by the transfer rate between the Coincidence Unit and the Host PC, which is considerably slower.

### 3.3.1 System Clock

The system clock is an 80 MHz clock. In general, it is generated on the Support Board in the Coincidence Unit (although it can be generated on the Support Board in a Detector Unit such as in the Small System), and then buffered through the rest of the system. Propagation delays will introduce skewing, therefore each FPGA that outputs data will also output a copy of the system clock that is synchronized with its output data signals. In general, each board in the system regenerates the clock using a phase-locked loop (PLL) in order to maintain signal quality and to minimize phase drift.

Fig. 3.7: System level timing signals.

### 3.3.2 Time Slice Boundary

The rising edge of the time slice boundary defines the beginning of a time slice. The width of the pulse is one system clock cycle, and the period is eight system clock cycles (for "short" event word mode) or sixteen system clock cycles (for "long" event word mode). In general, it is generated on the Support Board in the Coincidence Unit (although it can be generated on the Support Board in a Detector Unit such as in the Small System), and then buffered through the

rest of the system. Propagation delays will introduce skewing; therefore each FPGA that outputs data will also output a copy of the time slice boundary that is synchronized with its output data signals.

#### 3.3.3 Time Slice

The system divides time into small, fixed length time slices (100-200 ns or 8-16 clocks). All individual data processing operations must occur within a single time slice, which implies that only singles event words that occur in the same time slice can be combined to form a coincident event. While it can take significantly longer than one time slice to fully process a single event, the system is pipelined so that the processing is divided into smaller operations that each can be completed in a single time slice. It takes one time slice to transfer a singles event word.

# 3.4 Firmware & Software Structures

{Write this after you've written the corresponding section for the Developers Guide?}

The OpenPET firmware and software structures are based on a computer network tree topology. The configuration strategy needs to fulfill the following two basic requirements:

- (1) Compatibility with different types of detector modules (e.g. single analog channel addressing, single crystal addressing for a conventional block detector, etc.);

- (2) Compatibility with different sized systems (e.g., Small, Standard and Large Systems).

In addition, the addressing strategy needs to be implementable, flexible and reliable.

#### 3.4.1 Standard System

#### 3.4.2 Large System

#### 3.4.3 Small System

As described earlier (*Small System* (page 10)), the OpenPET system can also be configured as a Small System. In a Small System, a support board is configured as a Coincidence Detector Unit Controller (CDUC), which interfaces with the detector boards and performs coincidence functions. Basically the CDUC performs the functions of both the CUC and DUC. The initial firmware and software for the first release has been developed for a Small System. The configuration for a Small System is shown in Figure ?.

Fig. 3.8: Standard system firmware and software structure. (Add Host PC Interface Board, like Fig. 6 Developer Guide.)

# Getting Started - Small System Oscilloscope Mode

# 4.1 Getting Hardware

The OpenPET system uses a custom Support Crate that is similar to a VME crate (see *Support Crate* (page 7)). Support Crates should be purchased through Elma: Support Crate Chassis, part number 12V12XXX78N2VCGX-LBL, http://openpet.lbl.gov/purchase/.

The OpenPET PC boards can be purchased from Terasic through their OpenPET website at http://www.openpet.terasic.com. For a small system in the first release, each Detector Unit (see *Detector Unit* (page 7)) requires the following OpenPET boards:

- 1 Support Board

- 1-8 16-Channel Detector Boards

You also need the following additional components:

- 1 Host PC with a Windows 7 or Windows 10 operating system.

- 1 QuickUSB module: Bitwise Systems, part number QUSB2, http://www.bitwisesys.com/qusb2-p/qusb2.htm.

- 1 standard USB cable

- 1 USB-Blaster Cable: Terasic, Digi-Key part number P0302-ND, http://www.digikey.com/product-highlights/us/en/terasic-usb-blaster-cable/3718.

- Multiplexer Board/Coincidence Interface Board, http://www.openpet.terasic.com (only for Standard System)

The QuickUSB module is a small PC board that contains circuitry to provide high-speed USB 2.0 capability. It is plugged into either the Host PC Interface Board or the Support Board. The USB-Blaster cable interfaces between a USB port on the Host PC to the Altera main FPGA on the Support Board, so configuration data can be sent from the PC to the FPGAs. More detailed instructions are provided in the following sections.

# 4.2 Assembling the Hardware

**Warning:** All OpenPET parts are Electrostatic Sensitive Devices. Connect ground wire before touching any ESD.

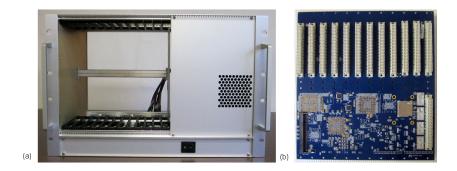

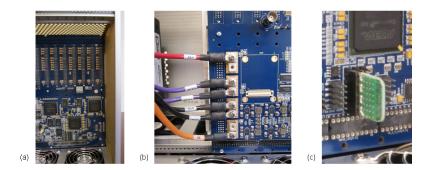

Once you receive the parts for an OpenPET support crate, some minor assembly is required. Fig. 4.1 shows the two main components: the empty Support Crate and the Support Board. In addition, you will receive a small custom jumper board (see Fig. 4.2c). You will also need a standard power cable for the crate, M2.5 x 12 mm Phillips head screws, M4 x 5 mm Phillips head screws, and appropriate screw drivers.

The first assembly step is to attach the Support Board to the crate. From the back side of the crate, align the screw holes on the Support Board to those on the Support Crate and secure it using M2.5 x 12 mm Phillips head screws. We recommend using at least 3 screws on the top, middle and bottom rows. It is also useful to place a piece of paper across the fans during assembly so any dropped screws don't fall into them. When the board is properly aligned, there should be about a 4 mm gap between the right edge of the Support Board and the right side of the Support Crate (Fig. 4.2a).

Fig. 4.1: (a) Empty Support Crate viewed from the front. (b) Support Board viewed from the front.

Once the Support Board is secured on the crate, you need to attach the power cables. The power cables and Support Board connectors are labeled. From bottom to top, the power cables are -5 V (orange cable), ground (black cables), +3.3 V (purple cables) and +5 V (red cable), as shown in Fig. 4.2b. Secure these power cables on to their respective Support Board connectors using M4 x 5 mm Phillips head screws. You may need to feed each screw through the power cable lug nut before attaching it to the Support Board, since the lug nuts fit tightly. In addition, there is a small bundle of cables that can be used for monitoring but these cables are not needed.

Finally you need to plug the custom small jumper board into the back of the Support Board. It plugs in to the connector just to the right of the Jtag connector (see Fig. 4.2c). Specifically, board plugs into the left column of pins on the connector (which is marked main, 58, 62, 65, 68). This jumper board identifies that the Jtag should communicate with the main FPGA on the Support Board.

The Support Board is shipped with the board receiving its system clock locally as set by a jumper J10 shorting pin 1 and 2 as shown in Fig. 4.3a, which is the setting for a Small System SB (i.e., DU in Fig. 3.4) and the master SB in a Standard System (i.e., CU in Fig. 3.5). The slave SB in a Standard System (i.e., DUs in Fig. 3.5) will need the jumper J10 shorting pin 2 and 3 as shown in Fig. 4.3b, which set the SB to receive its system clock from the CU instead of locally.

The fully assembled Support Crate is shown in Fig. 4.4.

Fig. 4.2: (a) Close up of the small gap ( $\sim$ 4 mm) between the Support Crate and the edge of the Support Board when assembled properly. (b) Close up of the power cables attached to the back of the Support Board. (c) Close up of the jumper board plugged into the back of the Support Board.

Fig. 4.3: (a) Jumper J10 on the SB shorting on pin 1 and 2 for a Small System and CU in a Standard System. (b) Jumper J10 on the SB shorting on pin 2 and 3 for the DUs in a Standard System.

Fig. 4.4: The assembled OpenPET Support Crate viewed from the (a) front and (b) back.

# 4.3 Downloading the Software and Firmware

#### 4.3.1 Installing QuickUSB

The OpenPET system requires the use of a QuickUSB module to provide high-speed USB 2.0 capability. You can purchase this online through Bitwise systems at http://www.bitwisesys.com/qusb2-p/qusb2.htm (product code QUSB2). In addition to the hardware module, this includes the QuickUSB library with a driver, interface DLL, and example programs for Linux, MacOSX and Windows. In addition, you will need a USB cable. However, you do not need to buy the QuickUSB Adapter Board as Bitwise implies.

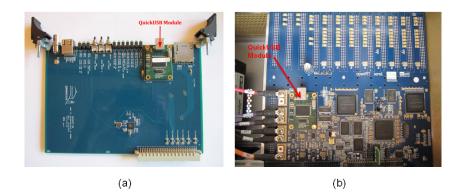

First, you need to mount the QuickUSB module onto either the Host PC Interface Board in the U3 connector or onto the Support Board in the U6 connector (Fig. 4.5). The system is designed to work with the QuickUSB module mounted in either (but not both) of these locations.

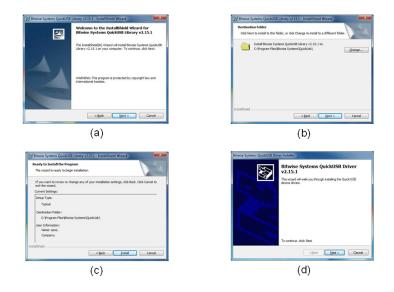

Next, you need to install the QuickUSB driver onto your Host PC. Browse and select the setup executable for the QuickUSB software (e.g., Desktop -> QuickUSB\_Installation -> Windows -> setup.exe). This will launch the Install-Shield Wizard in a new window (Fig. 4.6a). Step through the instructions by clicking the Next button at the bottom, agreeing to the software license agreement terms and defining the folder where the QuickUSB software should be installed (Fig. 4.6b). When the wizard is ready to begin installation of the library, click Install (Fig. 4.6c). The installation takes a few minutes and a status bar shows the progress. An additional window will then pop up that walks you through the installation of the QuickUSB device drivers (Fig. 4.6d). The InstallShield Wizard will indicate when the full installation is completed.

If you have further questions or problems with the installation, please refer to the Bitwise QuickUSB User Guide for details (e.g., http://www.bitwisesys.com/v/public/media/QuickUSB\_User\_Guide\_v2.15.2.pdf).

Once you have installed the QuickUSB module, you need to confirm it has the correct firmware model. OpenPET uses the default firmware model i.e., "QuickUSB QUSB2 Module v2.15.2 (Simple I/O)". If the version or the model is not correct, update the firmware using the QuickUSB Programmer (see Fig. 4.7). After you have successfully installed the correct firmware, you can confirm your installation by running the QuickUSB Diagnostics (see Fig. 4.8). The OpenPET system requires the firmware model "QuickUSB QUSB2 Module v2.15.2 (Simple I/O)" to configure

Fig. 4.5: QuickUSB module mounted onto the (a) Host PC Interface Board or (b) Support Board.

the QuickUSB module for the correct data transfer mode. For further details on this firmware model and configuration, please refer to the QuickUSB User Guide at http://www.bitwisesys.com/v/public/media/quickusb\_user\_guide.pdf.

#### 4.3.2 Installing Altera Tools

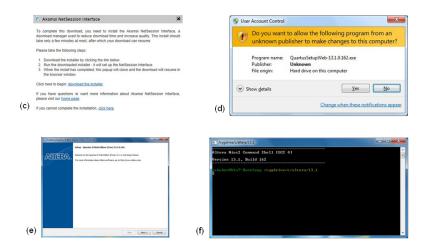

Even if you only plan to use the off the shelf OpenPET software and firmware, the OpenPET system requires the use of Altera design tools in order to load the appropriate firmware into the Support Board. These tools can be downloaded for free from the Altera Download Center website (e.g., https://www.altera.com/download/sw/dnl-sw-index.jsp, Fig. 4.9 a). From the Download Center, select to download the Quartus II Web Edition that is free and doesn't require a license.

On the Quartus II Web Edition download page Fig. 4.9 b, select release: 13.1 select the Windows operating system and the Akamai DLM Download Manager. Under the Individual Files tab, select the Quartus II Software and the Cyclone III, Cyclone IV device support. You can select additional options (such as the ModelSim-Altera Edition simulation tools), but they are not required to run OpenPET and they will lengthen the download time.

At this time, only Altera Quartus 13.1 is supported.

You are then required to log in with your username and password if you already have a myAltera account. If not, then create an account using your email address and complete the account registration information. Once your myAltera account has been created, you will be directed to your myAltera Home page. Select the Download Center link on the top right side of the page.

Once you have returned to the Download Center (Fig. 4.9 a), select the Quartus II Web Edition and specify the Windows operating system, DLM Download Manager, Quartus II Software, and the Cyclone III, Cyclone IV device support (if they aren't already specified). A separate Akamai NetSession Interface window will then pop up (Fig. 4.9 c) in which you should click Download on the installer and then Run to proceed with the software installation. You will have to agree to the End User License terms. A popup warning message will then appear in which you have to confirm that you want to open the executable file (e.g., QuartusSetupWeb-13.10.163.exe) from the Internet. You will then have to confirm that you want to allow this program to make changes to your computer (Fig. 4.9 d).

Fig. 4.6: Bitwise Systems QuickUSB Library v2.15.2 InstallShield Wizard: a) welcome window, (b) destination folder window, (c) installing the library window, and (d) installing the driver window.

| <b>8</b> Q   | uickUSB Pi      | rogrammer       | _                      |            | ×    |

|--------------|-----------------|-----------------|------------------------|------------|------|

| <u>F</u> ile | <u>O</u> ptions | <u>H</u> elp    |                        |            |      |

| _ General    |                 |                 |                        |            |      |

| M            | odule           | QUSB-0 💌        |                        |            |      |

| De           | escription      | kUSB QUSB2 Modu | ule <mark>v2.15</mark> | .2 (Simple | 1/0] |

| Public SN    |                 | 9105            |                        |            |      |

| Pr           | ivate SN        | 9105            |                        |            |      |

|              |                 |                 |                        |            |      |

|              |                 |                 |                        |            |      |

Fig. 4.7: QuickUSB Programmer used to program the QuickUSB module with the correct firmware: QuickUSB QUSB2 Module v2.15.2 (Simple I/O).

| QuickUsbDiagCs v2.15. | 1                       |                            | - 0             |

|-----------------------|-------------------------|----------------------------|-----------------|

| e Help                |                         |                            |                 |

| ne Serial Firmware    | Version Firmware Model  |                            |                 |

| iickUSB Modules       | QuickUSB QUSB2 Mod      | ula u2 15 2 (Simple 170)   |                 |

| 2030-0 3103 2.13.2    | QUICKUSE QUSEZ MOU      | ule vz. 15.2 (5111ple 170) |                 |

|                       |                         |                            |                 |

| eral Command Data     | Streaming Ports RS232 S | PI EPCS I2C Se             | ttings Defaults |

| ettings               |                         |                            |                 |

| P2CFG/EP6CFG          | 15 MSB                  | 87 LSB                     | 0<br>1          |

| URDWIDE               |                         |                            |                 |

| ataAddress            |                         |                            |                 |

| FOPolar/IFCONFIG      |                         |                            |                 |

| PGATYPE               |                         |                            |                 |

| usSpeed/CPUCUNFIG     |                         |                            |                 |

| JRTECFG/SPICUNFIG     |                         |                            |                 |

| aveHFU                |                         |                            |                 |

| CIL                   |                         |                            |                 |

| EA/IUA                |                         |                            |                 |

| FRNDR                 |                         |                            | ) 0x0000        |

| EC/IUC                |                         |                            | 0x0000          |

| EDVIUD                |                         |                            | 0x0000          |

| EE/IUE                |                         |                            | 0x0000          |

| JRTACEG/PORTCCEG      |                         |                            | 0x0000          |

| NFLAGSAB/CD           |                         |                            | 0x0000          |

|                       |                         |                            |                 |

Fig. 4.8: QuickUsb Diagnostics used to confirm the QuickUSB module with the correct firmware: QuickUSB QUSB2 Module v2.15.2 (Simple I/O).

Finally the Quartus II Web Edition Setup Wizard window will appear and step you through the installation (Fig. 4.9 e). You will have to agree to a License Agreement again as well as specify the installation directory (e.g., C:altera13.1). Then you should make sure that the components selected for installation are correct (e.g., Quartus II Software and Cyclone III/IV) and that you have the available disk space specified in the Summary. Once you start the installation, a status bar will show its progress. Once the Setup has finished installing the Altera tools, you can create shortcuts on your Desktop and launch Quartus II (Fig. 4.9 f).

If you have further questions or problems with the installation, please refer to the Altera support website (http://www.altera.com/support/spt-index.html) for user information. For specific instructions on how to use these Altera tools with the OpenPET system, see *Installing OpenPET Firmware & Software* (page 31).

#### 4.3.3 Installing USB-Blaster Driver

The USB-Blaster cable interfaces between a USB port on your Host PC and the Altera main FPGA on the Support Board. It allows configuration data to be sent from the Host PC to the FPGAs.

You must install the Altera USB-Blaster or USB-Blaster II driver before you can use the program devices with the Quartus II software. These drivers are automatically copied to the drivers folder within the Altera folder during the installation described in the previous section. However, it needs to be installed at first use. You will be prompted to install the driver the first time the USB-Blaster cable is plugged in. Whether you need to install the USB-Blaster or USB-Blaster II driver depends on your cable. Please see the step-by-step Altera instructions for this driver installation at http://www.altera.com/download/drivers/usb-blaster/dri-usb-blaster-vista.html.

Fig. 4.9: Altera Tools installation windows: (a) download center window, (b) Quartus II Web Edition window, (c) Akamai NetSession Interface window, (d) User Account Control confirmation window, (e) Quartus II Web Edition Setup Wizard window and (f) Altera Nios2 Command Shell window.

#### 4.3.4 Installing Ethernet

OpenPET also supports the capability of using Ethernet to configure and gather data from the system. You can connect your workstation to OpenPET Ethernet port on the HostPC Interface Board using a RJ45 cross-over cable or a (standard) straight-through cable with a switch in between. Both methods were tested. The network switch used was Netgear GS105.

To set up, open the Local Area Connection properties window for the connected Ethernet port (Fig. 4.10). Select Internet Protocol version 4.

After selecting the correct protocol, click on the Properties button. The window shown in Fig. 4.11 will open. Here, the OpenPET IP address is set. Select "Use the following IP address" and copy the values shown for the IP address, Subnet mask, and Default gateway.

Next, click on the Advanced button and the Advanced TCP/IP Settings window will open. Navigate to the DNS tab and select the settings shown in Fig. 4.12.

Also, disable NetBOIS over TCP/IP in the WINS tab as shown in Fig. 4.13.

After the IP settings are done, if you would like to use Jumbo frames to increase the throughput of your ethernet, go back to the Local Area Connection properties window (Fig. 4.10). Click on the top right Configure button and navigate to the Advanced tab (Fig. 4.14). Select the Jumbo Packet property as shown and the correct value.

It might be desirable to to use static ARP in order to reduce unneeded broadcasts on your data acquisition port. Open a command line prompt with administrator privileges and type:

C:\> arp -s 10.10.10.2 12-55-55-00-01-28 10.10.10.1

where 10.10.10.2 is your destination IP (OpenPET Chassis), 12-55-55-00-01-28 is the MAC address of OpenPET HostPC PHY, and 10.10.10.1 is the IP address of your workstation.

| 🖳 Local Area Connection 2 Properties 📃 💌                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Networking Sharing                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Connect using:                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Intel(R) PRO/1000 EB Network Connection with I/O Acce                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Configure                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| <ul> <li>Client for Microsoft Networks</li> <li>QoS Packet Scheduler</li> <li>File and Printer Sharing for Microsoft Networks</li> <li>Internet Protocol Version 6 (TCP/IPv6)</li> <li>Internet Protocol Version 4 (TCP/IPv4)</li> <li>Link-Layer Topology Discovery Mapper I/O Driver</li> <li>Link-Layer Topology Discovery Responder</li> </ul> |  |  |  |  |

| I <u>n</u> stall <u>U</u> ninstall P <u>r</u> operties                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Description<br>Allows your computer to access resources on a Microsoft<br>network.                                                                                                                                                                                                                                                                 |  |  |  |  |

| OK Cancel                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

Fig. 4.10: Local Area Connection properties window with the desired TCP/IPv4 selected.

| Internet Protocol Version 4 (TCP/IPv4)                                                                                                                                          | Properties 💦 💽 💌    |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|

| General                                                                                                                                                                         |                     |  |  |  |

| You can get IP settings assigned automatically if your network supports this capability. Otherwise, you need to ask your network administrator for the appropriate IP settings. |                     |  |  |  |

| 💿 Obtain an IP address automatical                                                                                                                                              | у                   |  |  |  |

| • Use the following IP address:                                                                                                                                                 |                     |  |  |  |

| IP address: 10 . 10 . 10 . 1                                                                                                                                                    |                     |  |  |  |

| S <u>u</u> bnet mask:                                                                                                                                                           | 255 . 255 . 255 . 0 |  |  |  |

| Default gateway:                                                                                                                                                                | 10 . 10 . 10 . 1    |  |  |  |

| Obtain DNS server address automatically                                                                                                                                         |                     |  |  |  |

| O Use the following DNS server addresses:                                                                                                                                       |                     |  |  |  |

| Preferred DNS server:                                                                                                                                                           |                     |  |  |  |

| <u>A</u> lternate DNS server:                                                                                                                                                   | · · ·               |  |  |  |

| Vaļidate settings upon exit                                                                                                                                                     | Ad <u>v</u> anced   |  |  |  |

|                                                                                                                                                                                 | OK Cancel           |  |  |  |

Fig. 4.11: Shows the IP address configuration for OpenPET

| Advanced TCP/IP Settings                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------|

| IP Settings DNS WINS                                                                                                              |

| D <u>N</u> S server addresses, in order of use:                                                                                   |

| t<br>l                                                                                                                            |

| Add Edit Remove                                                                                                                   |

| The following three settings are applied to all connections with TCP/IP<br>enabled. For resolution of unqualified names:          |

| <ul> <li>Append primary and connection specific DNS suffixes</li> <li>Append parent suffixes of the primary DNS suffix</li> </ul> |

| Append these DNS suffixes (in order):                                                                                             |

| t                                                                                                                                 |

| Add Edit Remove                                                                                                                   |

| DNS <u>s</u> uffix for this connection:                                                                                           |

| Register this connection's addresses in DNS           Use this connection's DNS suffix in DNS registration                        |

| OK Cancel                                                                                                                         |

Fig. 4.12: Shows DNS settings

| Advanced TCP/IP Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ? 💌                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| IP Settings DNS WINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |

| <u>W</u> INS addresses, in order of use:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |

| <u>A</u> dd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Remo <u>v</u> e       |

| If LMHOSTS lookup is enabled, it applies to all<br>TCP/IP is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | connections for which |

| Enable LMHOSTS lookup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Import LMHOSTS        |

| <ul> <li>NetBIOS setting</li> <li>Default:</li> <li>Use NetBIOS setting from the DHCP set is used or the DHCP server does not pienable NetBIOS over TCP/IP.</li> <li>Enable NetBIOS over TCP/IP</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

| Oisable NetBIOS over TCP/IP     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O |                       |

| (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OK Cancel             |

Fig. 4.13: Shows WINS settings

| Intel(R) PRO/1000 EB Network Connection with I/O Acceleration # 🔤                                                                                                                                                                                                                                                               |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| General Advanced Driver Details Power Management                                                                                                                                                                                                                                                                                |  |  |  |

| The following properties are available for this network adapter. Click<br>the property you want to change on the left, and then select its value<br>on the right.                                                                                                                                                               |  |  |  |

| Property: ⊻alue:                                                                                                                                                                                                                                                                                                                |  |  |  |

| Adaptive Inter-Frame Spacing<br>Enable PME<br>Flow Control<br>Gigabit Master Slave Mode<br>Interrupt Moderation Rate<br>IPv4 Checksum Offload<br>Uumbo Packet<br>Large Send Offload v2 (IPv4)<br>Large Send Offload v2 (IPv6)<br>Link Speed & Duplex<br>Locally Administered Address<br>Log Link State Event<br>Priority & VLAN |  |  |  |

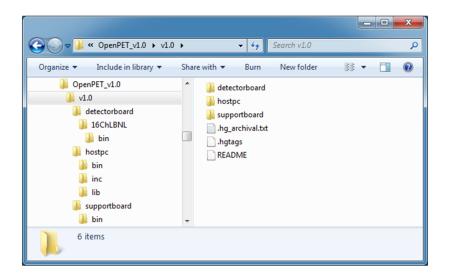

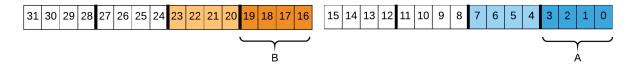

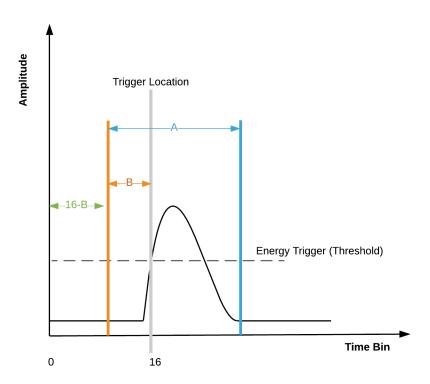

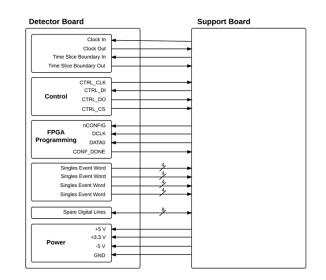

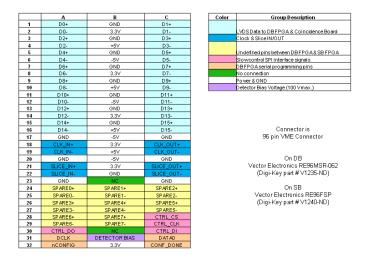

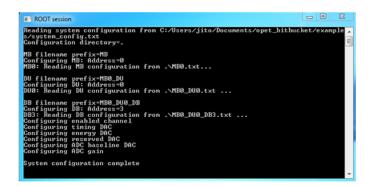

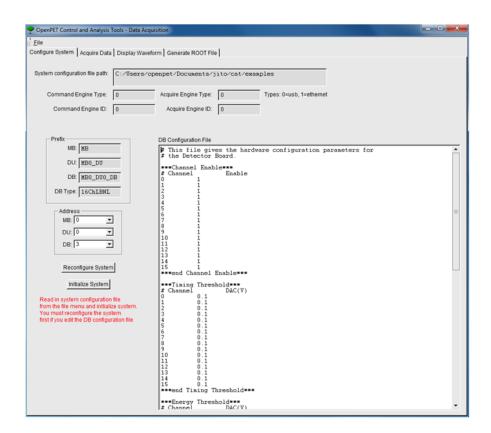

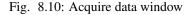

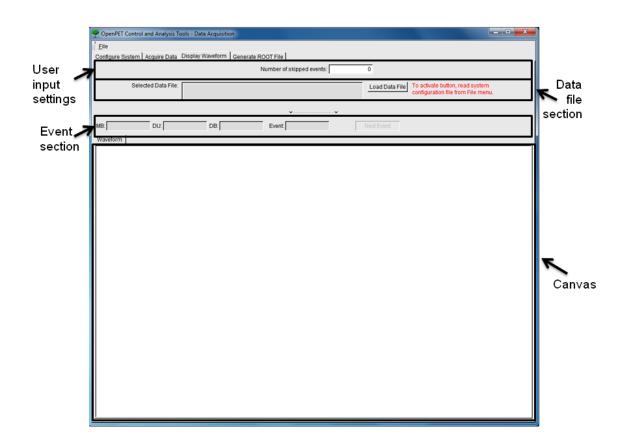

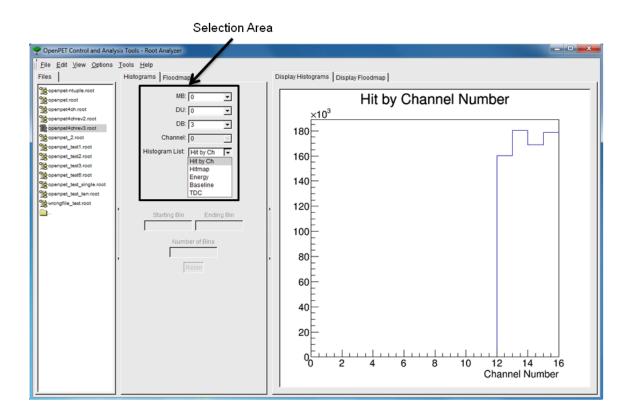

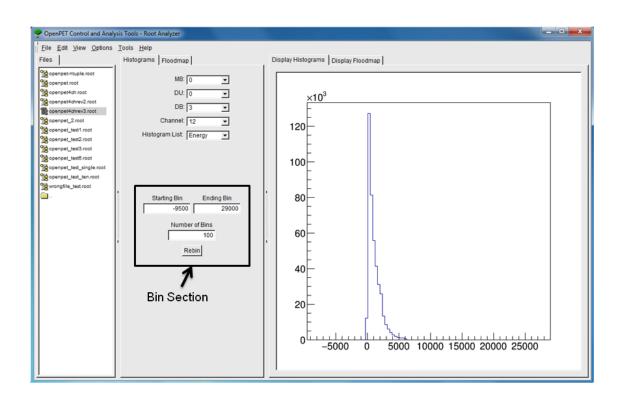

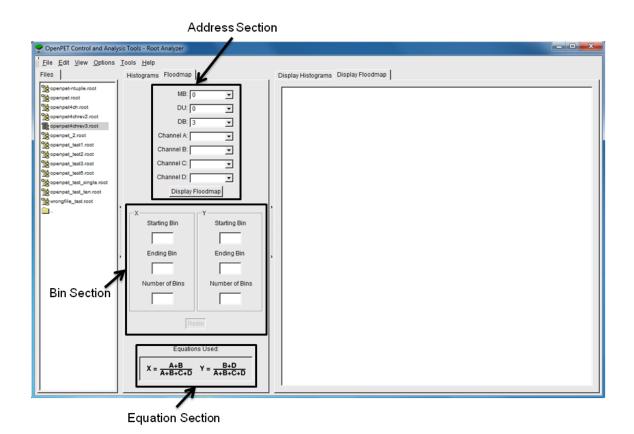

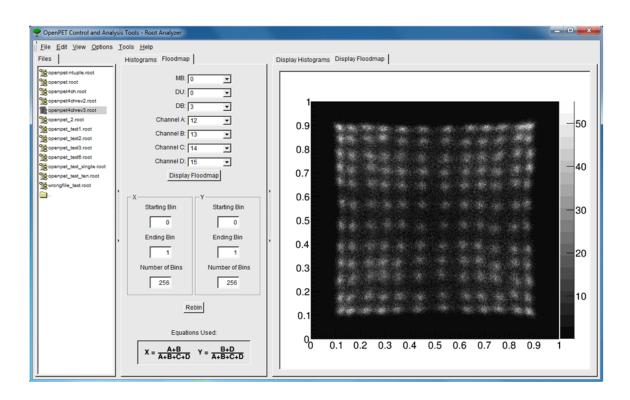

| OK Cancel                                                                                                                                                                                                                                                                                                                       |  |  |  |