# **The PoC-Library Documentation**

Release 1.0.0

Patrick Lehmann, Thomas B. Preusser, Martin Zabel

# Contents

| 1 | News |                                     |

|---|------|-------------------------------------|

|   | 1.1  | 13.05.2016 - PoC 1.0.0 was released |

| 2 |      | the PoC-Library 5                   |

|   | 2.1  | What is PoC?                        |

|   | 2.2  | Quick Start Guide                   |

|   | 2.3  | Using PoC                           |

|   | 2.4  | IP Core Documentations              |

|   | 2.5  | Third Party Libraries               |

|   | 2.6  | Constraint Files                    |

|   | 2.7  | References                          |

|   |      | Get Involved                        |

|   | 2.9  | Change Log                          |

|   | 2.10 | Apache License 2.0                  |

This library is published and maintained by **Chair for VLSI Design**, **Diagnostics and Architecture** - Faculty of Computer Science, Technische Universität Dresden, Germany https://tu-dresden.de/ing/informatik/ti/vlsi

TECHNISCHE UNIVERSITÄT DRESDEN

PoC - "Pile of Cores" provides implementations for often required hardware functions such as Arithmetic Units, Caches, Clock-Domain-Crossing Circuits, FIFOs, RAM wrappers, and I/O Controllers. The hardware modules are typically provided as VHDL or Verilog source code, so it can be easily re-used in a variety of hardware designs.

All hardware modules use a common set of VHDL packages to share new VHDL types, sub-programs and constants. Additionally, a set of simulation helper packages eases the writing of testbenches. Because PoC hosts a huge amount of IP cores, all cores are grouped into sub-namespaces to build a better hierarchy.

Various simulation and synthesis tool chains are supported to interoperate with PoC. To generalize all supported free and commercial vendor tool chains, PoC is shipped with a Python based infrastructure to offer a command line based frontend.

Contents 1

2 Contents

| CHAPTER ' | 1 |

|-----------|---|

|-----------|---|

# **News**

# 1.1 13.05.2016 - PoC 1.0.0 was released.

Lorem ipsum dolor sit amet, consetetur sadipscing elitr, sed diam nonumy eirmod tempor invidunt ut labore et dolore magna aliquyam erat, sed diam voluptua. At vero eos et accusam et justo duo dolores et ea rebum. Stet clita kasd gubergren, no sea takimata sanctus est Lorem ipsum dolor sit amet. Lorem ipsum dolor sit amet, consetetur sadipscing elitr, sed diam nonumy eirmod tempor invidunt ut labore et dolore magna aliquyam erat, sed diam voluptua. At vero eos et accusam et justo duo dolores et ea rebum. Stet clita kasd gubergren, no sea takimata sanctus est Lorem ipsum dolor sit amet

Chapter 1. News

# Cite the PoC-Library

The PoC-Library hosted at GitHub.com. Please use the following biblatex entry to cite us:

```

# BibLaTex example entry

@online{poc,

title={{PoC - Pile of Cores}},

author={{Chair of VLSI Design, Diagnostics and Architecture}},

organization={{Technische Universität Dresden}},

year={2016},

url={https://github.com/VLSI-EDA/PoC},

urldate={2016-10-28},

}

```

# 2.1 What is PoC?

PoC - "Pile of Cores" provides implementations for often required hardware functions such as Arithmetic Units, Caches, Clock-Domain-Crossing Circuits, FIFOs, RAM wrappers, and I/O Controllers. The hardware modules are typically provided as VHDL or Verilog source code, so it can be easily re-used in a variety of hardware designs.

All hardware modules use a common set of VHDL packages to share new VHDL types, sub-programs and constants. Additionally, a set of simulation helper packages eases the writing of testbenches. Because PoC hosts a huge amount of IP cores, all cores are grouped into sub-namespaces to build a better hierarchy.

Various simulation and synthesis tool chains are supported to interoperate with PoC. To generalize all supported free and commercial vendor tool chains, PoC is shipped with a Python based Infrastruture to offer a command line based frontend.

#### The PoC-Library pursues the following five goals:

- independence in the platform, target, vendor and tool chain

- generic, efficient, resource sparing and fast implementations of IP cores

- optimized for several device architectures, if suitable

- supportive scripts to ease the IP core handling with all supported vendor tools on all listed operating systems

- ship all IP cores with testbenches for local and online verification

## In detail the PoC-Library is:

- synthesizable for ASIC and FPGA devices, e.g. from Altera, Lattice, Xilinx, ...,

- supports a wide range of simulation and synthesis tool chains, and is

- · executable on several host platforms: Darwin, Linux or Windows.

This is achieved by using generic HDL descriptions, which work with most synthesis and simulation tools mentioned above. If this is not the case, then PoC uses vendor or tool dependent work-arounds. These work-arounds can be different implementations switched by VHDL *generate* statements as well as different source files containing modified implementations.

One special feature of PoC is it, that the user has not to take care of such implementation switchings. PoC's IP cores decide on their own what's the *best* implementation for the chosen target platform. For this feature, PoC implements a configuration package, which accepts a well-known development board name or a target device string. For example a FPGA device string is decoded into: vendor, device, generation, family, subtype, speed grade, pin count, etc. Out of these information, the PoC component can for example implement a vendor specific carry-chain description to speed up an algorithm or group computation units to effectively use 6-input LUTs.

# 2.1.1 What is the History of PoC?

In the past years, a lot of "IP cores" were developed at the chair of VLSI design <sup>1</sup>. This lose set of HDL designs was gathered in an old-fashioned CVS repository and grow over the years to a collection of basic HDL implementations like ALUs, FIFOs, UARTs or RAM controllers. For their final projects (bachelor, master, diploma thesis) students got access to PoC, so they could focus more on their main tasks than wasting time in developing and testing basic IP implementations from scratch. But the library was initially for internal and educational use only.

As a university chair for VLSI design, we have a wide range of different FPGA prototyping boards from various vendors and device families as well as generations. So most of the IP cores were developed for both major FPGA vendor platforms and their specific vendor tool chains. The main focus was to describe hardware in a more flexible and generic way, so that an IP core could be reused on multiple target platforms.

As the number of cores increased, the set of common functions and types increased too. In the end PoC is not only a collection of IP cores, its also shipped with a set of packages containing utility functions, new types and type conversions, which are used by most of the cores. This makes PoC a *library*, not only a *collection* of IPs.

As we started to search for ways to publish IP cores and maybe the whole PoC-Library, we found several platforms on the Internet, but none was very convincing. Some collective websites contained inactive projects, others were controlled by companies without the possibility to contribute and the majority was a long list of private projects with at most a handful of IP cores. Another disagreement were the used license types for these projects. We decided to use the Apache License, because it has no copyleft rule, a patent clause and allows commercial usage.

We transformed the old CVS repository into three Git repositories: An internal repository for the full set of IP cores (incl. classified code), a public one and a repository for examples, called PoC-Examples, both hosted on GitHub. PoC itself can be integrated into other HDL projects as a library directory or a Git submodule. The preferred usage is the submodule integration, which has the advantage of linked repository versions from hosting Git and the submodule Git. This is already exemplified by our PoC-Examples repository.

## 2.1.2 Which Tool Chains are supported?

The PoC-Library and its Python-based infrastructure currently supports the following free and commercial vendor tool chains:

- Synthesis Tool Chains:

- Altera Quartus Tested with Quartus-II 13.0. Tested with Quartus Prime 15.1.

- Lattice Diamond Tested with Diamond 3.6.

- Xilinx ISE Only ISE 14.7 inclusive Core Generator 14.7 is supported.

- Xilinx PlanAhead Only PlanAhead 14.7 is supported.

<sup>&</sup>lt;sup>1</sup> The PoC-Library is published and maintained by the **Chair for VLSI Design, Diagnostics and Architecture** - Faculty of Computer Science, Technische Universität Dresden, Germany http://tu-dresden.de/inf/vlsi-eda

- Xilinx Vivado Tested with Vivado 2015.4. Due to a limited VHDL language support compared to ISE 14.7, some PoC IP cores need special work arounds. See the synthesis documention section for Vivado for more details.

- Simulation Tool Chains:

- Aldec Active-HDL Tested with Active-HDL Student-Edition 10.3 Tested with Active-HDL Lattice Edition 10.2

- Cocotb with Mentor QuestaSim backend Tested with Mentor QuestaSim 10.4d

- Mentor Graphics QuestaSim/ModelSim Tested with ModelSim Altera Edition 10.3d and ModelSim Altera Starter Edition 10.3d Tested with Mentor QuestaSim 10.4d

- Xilinx ISE Simulator Tested with ISE Simulator (iSim) 14.7. The Python infrastructure supports

isim, but PoC's simulation helper packages and testbenches rely on VHDL-2008 features, which are

not supported by isim.

- Xilinx Vivado Simulator Tested with Vivado Simulator (xsim) 2016.1. The Python infrastructure supports xsim, but PoC's simulation helper packages and testbenches rely on VHDL-2008 features, which are not fully supported by xsim, yet.

- **GHDL** + **GTKWave** Tested with GHDL 0.34dev and GTKWave 3.3.70 Due to ungoing development and bugfixes, we encourage to use the newest GHDL version.

# 2.1.3 Why should I use PoC?

Here is a brief list of advantages:

- We explicitly use the wording *PoC-Library* rather then *collection*, because PoC's packages and IP cores build an ecosystem. Complex IP cores are build on-top of basic IP cores they are no lose set of cores. The cores offer a clean interface and can be configured by many generic parameters.

- PoC is target independent: It's possible to switch the target device or even the device vendor without switching the IP core.

#### Todo

Use a well tested set of packages to ease the use of VHDL

Use a well tested set of simulation helpers

Run testbenches in various simulators.

Run synthesis tests in varous synthesis tools.

Compare hardware usage for different target platfroms.

Supports simulation with vendor primitive libraries, ships with script to pre-compile vendor libraries.

Vendor tools have bugs, check you IP cores when a new tool release is available, before changing code base

## 2.1.4 Who uses PoC?

PoC has a related Git repository called PoC-Examples on GitHub. This repository hosts a list of example and reference implementations of the PoC-Library. Additional to reading an IP cores documention and viewing its characteristic stimulus waveform in a simulation, it can helper to investigate an IP core usage example from that repository.

- The Q27 Project 27-Queens Puzzle: Massively Parellel Enumeration and Solution Counting

- Reconfigurable Cloud Computing Framework (RC2F) An FPGA computing framework for virtualization and cloud integration.

2.1. What is PoC?

- PicoBlaze-Library The PicoBlaze-Library offers several PicoBlaze devices and code routines to extend a common PicoBlaze environment to a little System on a Chip (SoC or SoFPGA).

- PicoBlaze-Examples A SoFPGA reference implementation, based on the PoC-Library and the PicoBlaze-Library.

# 2.2 Quick Start Guide

This **quick start guide** gives a fast and simple introduction into PoC. All topics can be found in the Using PoC section with much more details and examples.

## Contents of this Page

- Requirements and Dependencies

- Download

- Configuring PoC on a Local System

- Integration

- Run a Simulation

- Run a Synthesis

- Updating

# 2.2.1 Requirements and Dependencies

The PoC-Library comes with some scripts to ease most of the common tasks, like running testbenches or generating IP cores. PoC uses Python 3 as a platform independent scripting environment. All Python scripts are wrapped in Bash or PowerShell scripts, to hide some platform specifics of Darwin, Linux or Windows. See Requirements for further details.

#### **PoC** requires:

- A supported synthesis tool chain, if you want to synthesise IP cores.

- A supported simulator too chain, if you want to simulate IP cores.

- The **Python 3** programming language and runtime, if you want to use PoC's infrastructure.

- A shell to execute shell scripts:

- Bash on Linux and OS X

- PowerShell on Windows

## PoC optionally requires:

- Git command line tools or

- Git User Interface, if you want to check out the latest 'master' or 'release' branch.

# PoC depends on third part libraries:

- · Cocotb A coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python.

- OS-VVM Open Source VHDL Verification Methodology.

- VUnit An unit testing framework for VHDL.

All dependencies are available as GitHub repositories and are linked to PoC as Git submodules into the PoC-Root\lib directory. See Third Party Libraries for more details on these libraries.

#### 2.2.2 Download

The PoC-Library can be downloaded as a zip-file (latest 'master' branch), cloned with git clone or embedded with git submodule add from GitHub. GitHub offers HTTPS and SSH as transfer protocols. See the Download page for further details. The installation directory is referred to as PoCRoot.

| Protocol | Git Clone Command                                            |

|----------|--------------------------------------------------------------|

| HTTPS    | git clonerecursive https://github.com/VLSI-EDA/PoC.git PoC   |

| SSH      | git clonerecursive ssh://git@github.com:VLSI-EDA/PoC.git PoC |

# 2.2.3 Configuring PoC on a Local System

To explore PoC's full potential, it's required to configure some paths and synthesis or simulation tool chains. The following commands start a guided configuration process. Please follow the instructions on screen. It's possible to relaunch the process at any time, for example to register new tools or to update tool versions. See Configuration for more details. Run the following command line instructions to configure PoC on your local system:

```

cd PoCRoot

.\poc.ps1 configure

```

Use the keyboard buttons: Y to accept, N to decline, P to skip/pass a step and Return to accept a default value displayed in brackets.

# 2.2.4 Integration

The PoC-Library is meant to be integrated into other HDL projects. Therefore it's recommended to create a library folder and add the PoC-Library as a Git submodule. After the repository linking is done, some short configuration steps are required to setup paths, tool chains and the target platform. The following command line instructions show a short example on how to integrate PoC.

## 1. Adding the Library as a Git submodule

The following command line instructions will create the folder lib\PoC\ and clone the PoC-Library as a Git submodule into that folder. ProjectRoot is the directory of the hosting Git. A detailed list of steps can be found at Integration.

```

cd ProjectRoot

mkdir lib | cd

git submodule add https://github.com:VLSI-EDA/PoC.git PoC

cd PoC

git remote rename origin github

cd ..\..

git add .gitmodules lib\PoC

git commit -m "Added new git submodule PoC in 'lib\PoC' (PoC-Library)."

```

#### 2. Configuring PoC

The PoC-Library should be configured to explore its full potential. See Configuration for more details. The following command lines will start the configuration process:

```

cd ProjectRoot

.\lib\PoC\poc.ps1 configure

```

#### 3. Creating PoC's my\_config.vhdl and my\_project.vhdl Files

The PoC-Library needs two VHDL files for its configuration. These files are used to determine the most suitable implementation depending on the provided target information. Copy the following two template files into your project's source folder. Rename these files to \*.vhdl and configure the VHDL constants in the files:

```

cd ProjectRoot

cp lib\PoC\src\common\my_config.vhdl.template src\common\my_config.vhdl

cp lib\PoC\src\common\my_project.vhdl.template src\common\my_project.vhdl

```

my\_config.vhdl defines two global constants, which need to be adjusted:

```

constant MY_BOARD : string := "CHANGE THIS"; -- e.g. Custom, ML505, KC705, Atlys

constant MY_DEVICE : string := "CHANGE THIS"; -- e.g. None, XC5VLX50T-1FF1136, EP2SGX90.

```

my\_project.vhdl also defines two global constants, which need to be adjusted:

```

constant MY_PROJECT_DIR : string := "CHANGE THIS"; -- e.g. d:/vhdl/myproject/, /home/me/proj

constant MY_OPERATING_SYSTEM : string := "CHANGE THIS"; -- e.g. WINDOWS, LINUX

```

Further informations are provided at Creating my\_config/my\_project.vhdl.

#### 4. Adding PoC's Common Packages to a Synthesis or Simulation Project

PoC is shipped with a set of common packages, which are used by most of its modules. These packages are stored in the PoCRoot\src\common directory. PoC also provides a VHDL context in common.vhdl, which can be used to reference all packages at once.

#### 5. Adding PoC's Simulation Packages to a Simulation Project

Simulation projects additionally require PoC's simulation helper packages, which are located in the PoCRoot\src\sim directory. Because some VHDL version are incompatible among each other, PoC uses version suffixes like \*.v93.vhdl or \*.v08.vhdl in the file name to denote the supported VHDL version of a file.

## 6. Compiling Shipped IP Cores

Some IP Cores are shipped are pre-configured vendor IP Cores. If such IP cores shall be used in a HDL project, it's recommended to use PoC to create, compile and if needed patch these IP cores. See Synthesis for more details.

## 2.2.5 Run a Simulation

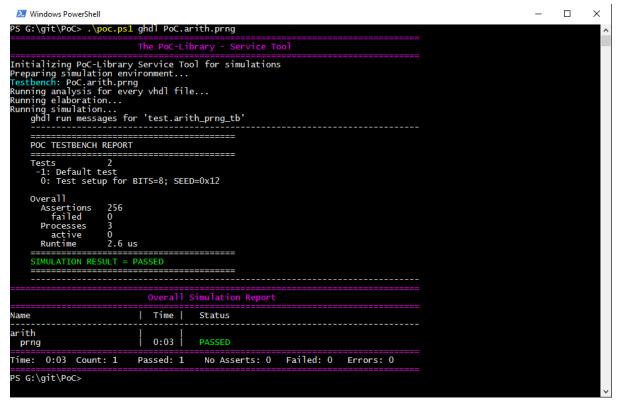

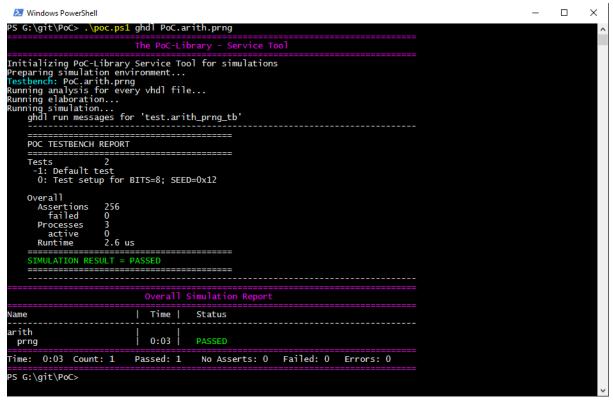

The following quick example uses the GHDL Simulator to analyze, elaborate and simulate a testbench for the module arith\_prng (Pseudo Random Number Generator - PRNG). The VHDL file arith\_prng.vhdl is located at PoCRoot\src\arith and virtually a member in the *PoC.arith* namespace. So the module can be identified by an unique name: PoC.arith.prng, which is passed to the frontend script.

#### **Example:**

```

cd PoCRoot

.\poc.ps1 ghdl PoC.arith.prng

```

The CLI command ghdl chooses *GHDL Simulator* as the simulator and passes the fully qualified PoC entity name PoC.arith.prng as a parameter to the tool. All required source file are gathered and compiled to an executable. Afterwards this executable is launched in CLI mode and its outputs are displayed in console:

Each testbench uses PoC's simulation helper packages to count asserts and to track active stimuli and checker processes. After a completed simulation run, an report is written to STDOUT or the simulator's console. Note the line SIMULATION RESULT = PASSED. For each simulated PoC entity, a line in the overall report is created. It lists the runtime per testbench and the simulation status (... ERROR, FAILED, NO ASSERTS or PASSED). See Simulation for more details.

## 2.2.6 Run a Synthesis

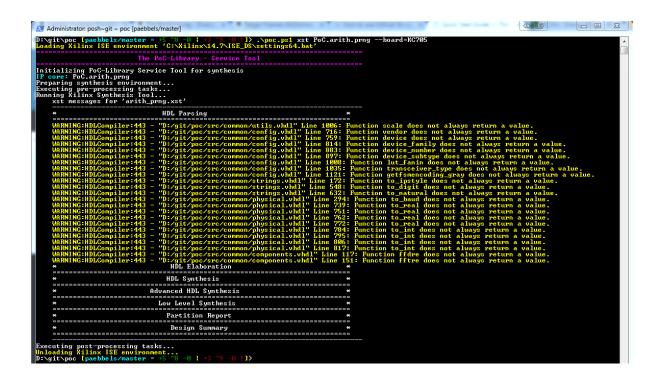

The following quick example uses the Xilinx Systesis Tool (XST) to synthesize a netlist for IP core arith\_prng (Pseudo Random Number Generator - PRNG). The VHDL file arith\_prng.vhdl is located at PoCRoot\src\arith and virtually a member in the *PoC.arith* namespace. So the module can be identified by an unique name: PoC.arith.prng, which is passed to the frontend script.

#### **Example:**

```

cd PoCRoot

.\poc.ps1 xst PoC.arith.prng --board=KC705

```

The CLI command xst chooses *Xilinx Synthesis Tool* as the synthesizer and passes the fully qualified PoC entity name PoC.arith.prng as a parameter to the tool. Additionally, the development board name is required to load the correct my\_config.vhdl file. All required source file are gathered and synthesized to a netlist.

# 2.2.7 Updating

The PoC-Library can be updated by using git fetch and git merge.

```

cd PoCRoot

# update the local repository

git fetch --prune

# review the commit tree and messages, using the 'treea' alias

git treea

# if all changes are OK, do a fast-forward merge

git merge

```

#### See also:

Running one or more testbenches The installation can be checked by running one or more of PoC's testbenches.

**Running one or more netlist generation flows** The installation can also be checked by running one or more of PoC's synthesis flows.

# 2.3 Using PoC

PoC can be used in several ways, if all Requirements are fulfilled. Chose one of the following integration kinds:

• Stand-Alone IP Core Library: Download PoC as archive file (\*.zip) from GitHub as latest branch copy or as tagged release file. IP cores can be copyed into one or more destination projects or the projects link to the selected IP core source files.

#### Advantages:

- Simple and fast setup, configuring PoC is optional.

- Needs less disk space than a Git repository.

- After a configuration, PoC's additional features: simulation, synthesis, etc. can be used.

## **Disadvantages:**

- Manual updating via download and file overwrites.

- Updated IP cores need to be copyed again into the destination project.

- Using different PoC versions in different projects is not possible.

- No possibility to contribute bugfixes and extensions via Git pull requests.

**Next steps:** 1. See Downloads for how to download a stand-alone version (\*.zip-file) of the PoC-Library. 2. See Configuration for how to configure PoC on a local system.

• Stand-Alone IP Core Library cloned from Git: Download PoC via git clone from GitHub as latest branch copy. IP cores can be copyed into one or more destination projects or the projects link to the selected IP core source files.

#### Advantages:

- Simple and fast setup, configuring PoC is optional.

- Access to the newest commits on a branch: New IP cores, new features, bugfixes.

- Fast and simple updates via git pull.

- After a configuration, PoC's additional features: simulation, synthesis, etc. can be used.

- Contribute bugfixes and extensions via Git pull requests.

## **Disadvantages:**

- Updated IP cores need to be copyed again into the destination project.

- Using different PoC versions in different projects is not possible

**Next steps:** 1. See Downloads for how to clone a stand-alone version of the PoC-Library. 2. See Configuration for how to configure PoC on a local system.

• Embedded IP Core Library as Git Submodule: Integrate PoC as a Git submodule into the destination projects Git repository.

#### Advantages:

- Simple and fast setup, configuring PoC is optional, but recommended.

- Access to the newest commits on a branch: New IP cores, new features, bugfixes.

- Fast and simple updates via git pull.

- After a configuration, PoC's additional features: simulation, synthesis, etc. can be used.

- Moreover, some PoC infrastructure features can be used in the hosting repository and project as well.

- Contribute bugfixes and extensions via Git pull requests.

- Version linking between hosting Git and PoC.

**Next steps:** 1. See Integration for how to integrate PoC as a Git submodule into an existing Git. 2. See Configuration for how to configure PoC on a local system.

# 2.3.1 Requirements

#### **Contents of this Page**

- Common requirements:

- Linux specific requirements:

- Optional Tools on Linux:

- Mac OS specific requirements:

- Optional Tools on Mac OS:

- Windows specific requirements:

- Optional Tools on Windows:

The PoC-Library comes with some scripts to ease most of the common tasks, like running testbenches or generating IP cores. We choose to use Python 3 as a platform independent scripting environment. All Python scripts are wrapped in Bash or PowerShell scripts, to hide some platform specifics of Darwin, Linux or Windows.

## **Common requirements:**

- Programming Languages and Runtime Environments:

- Python 3 (3.5):

- \* colorama

- \* py-flags

All Python requirements are listed in requirements.txt and can be installed via: sudo python3.5 -m pip install -r requirements.txt

- Synthesis tool chains:

- Altera Quartus 13.0 or

- Lattice Diamond or

- Xilinx ISE 14.7 <sup>1</sup> or

- Xilinx Vivado<sup>2</sup>

- · Simulation tool chains

- Aldec Active-HDL or

- Mentor Graphics ModelSim Altera Edition or

- Mentor Graphics QuestaSim or

- Xilinx ISE Simulator 14.7 or

- Xilinx Vivado Simulator 2016.1 3 or

- GHDL 0.34dev and GTKWave 3.3.70

## Linux specific requirements:

- Debian and Ubuntu specific:

- bash is configured as /bin/sh (read more) dpkg-reconfigure dash

#### **Optional Tools on Linux:**

- **Git** The command line tools to manage Git repositories. It's possible to extend the shell prompt with Git information.

- SmartGit A Git client to handle complex Git flows in a GUI.

- Generic Colouriser (grc) 1.9 Colorizes outputs of foreign scripts and programs. GRC is hosted on GitHub The latest \*.deb installation packages can be downloaded here.

<sup>&</sup>lt;sup>1</sup> Xilinx discontinued ISE since Oct. 2013. The last release was 14.7.

<sup>&</sup>lt;sup>2</sup> Due to numerous bugs in the Xilinx Vivado Synthesis (incl. 2016.1), PoC can offer only a restricted Vivado support. See PoC's Vivado branch for a set of workarounds. The list of issues is documented on the Known Issues page.

<sup>&</sup>lt;sup>3</sup> Due to numerous bugs in the Xilinx Simulator (incl. 2016.1), PoC can offer only a restricted Vivado support. The list of issues is documented on the Known Issues page.

## Mac OS specific requirements:

- Bash 4.3 Mac OS is shipped with Bash 3.2. Use Homebrew to install an up-to-date Bash brew install bash

- coreutils Mac OS' readlink program has a different behavior than the Linux version. The coreutils package installs a GNU readlink clone called greadlink. brew install coreutils

## **Optional Tools on Mac OS:**

- **Git** The command line tools to manage Git repositories. It's possible to extend the shell prompt with Git information.

- SmartGit or SourceTree A Git client to handle complex Git flows in a GUI.

- Generic Colouriser (grc) 1.9 Colorizes outputs of foreign scripts and programs. GRC is hosted on GitHub brew install Grc

# Windows specific requirements:

- **PowerShell 4.0** PowerShell shipped with Windows since Vista. It is a part if the Windows Management Framework. If the required version not already included in Windows, it can be downloaded from microsoft.com: WMF 4.0, WMF 5.0 (recommended).

- Allow local script execution (read more) Set-ExecutionPolicy RemoteSigned

- PowerShell Community Extensions (PSCX) 3.2 The latest PSCX can be downloaded from Power-ShellGallery

# **Optional Tools on Windows:**

- **Git** (**MSys-Git**) The command line tools to manage Git repositories.

- SmartGit or SourceTree A Git client to handle complex Git flows in a GUI.

- posh-git PowerShell integration for Git Installing posh-git with PsGet package manager: Install-Module posh-git

## 2.3.2 Downloading PoC

## **Contents of this Page**

- Downloading from GitHub

- Downloading via git clone

- On Linux

- On OS X

- On Windows

- Downloading via git submodule add

- On Linux

- On OS X

- On Windows

## **Downloading from GitHub**

The PoC-Library can be downloaded as a zip-file from GitHub. See the following table, to choose your desired git branch.

| Branch  | download link |

|---------|---------------|

| master  | zip-file      |

| release | zip-file      |

## Downloading via git clone

The PoC-Library can be downloaded (cloned) with git clone from GitHub. GitHub offers the transfer protocols HTTPS and SSH. You should use SSH if you have a GitHub account and have already uploaded an OpenSSH public key to GitHub, otherwise use HTTPS if you have no account or you want to use login credentials.

The created folder <GitRoot>PoC is used as <PoCRoot> in later instructions or on other pages in this documentation.

| Protocol | GitHub Repository URL                 |

|----------|---------------------------------------|

| HTTPS    | https://github.com/VLSI-EDA/PoC.git   |

| SSH      | ssh://git@github.com:VLSI-EDA/PoC.git |

#### On Linux

Command line instructions to clone the PoC-Library onto a Linux machine with HTTPS protocol:

```

cd GitRoot

git clone --recursive "https://github.com/VLSI-EDA/PoC.git" PoC

cd PoC

git remote rename origin github

```

Command line instructions to clone the PoC-Library onto a Linux machine machine with SSH protocol:

```

cd GitRoot

git clone --recursive "ssh://git@github.com:VLSI-EDA/PoC.git" PoC

cd PoC

git remote rename origin github

```

#### On OS X

Please see the Linux instructions.

#### On Windows

**Note:** All Windows command line instructions are intended for **Windows PowerShell**, if not marked otherwise. So executing the following instructions in Windows Command Prompt (**cmd.exe**) won't function or result in errors! See the Requirements section on where to download or update PowerShell.

Command line instructions to clone the PoC-Library onto a Windows machine with HTTPS protocol:

```

cd GitRoot

git clone --recursive "https://github.com/VLSI-EDA/PoC.git" PoC

cd PoC

git remote rename origin github

```

Command line instructions to clone the PoC-Library onto a Windows machine with SSH protocol:

```

cd GitRoot

git clone --recursive "ssh://git@github.com:VLSI-EDA/PoC.git" PoC

cd PoC

git remote rename origin github

```

**Note:** The option —recursive performs a recursive clone operation for all linked git submodules. An additional git submodule init and git submodule update call is not needed anymore.

## Downloading via git submodule add

The PoC-Library is meant to be integrated into other HDL projects (preferably Git versioned projects). Therefore it's recommended to create a library folder and add the PoC-Library as a git submodule.

The following command line instructions will create a library folder: file: 'lib' and clone PoC as a git submodule into the subfolder: file: '< ProjectRoot > libPoC'.

#### On Linux

Command line instructions to clone the PoC-Library onto a Linux machine with HTTPS protocol:

```

cd ProjectRoot

mkdir lib

git submodule add "https://github.com/VLSI-EDA/PoC.git" lib/PoC

cd lib/PoC

git remote rename origin github

cd ../..

git add .gitmodules lib/PoC

git commit -m "Added new git submodule PoC in 'lib/PoC' (PoC-Library)."

```

Command line instructions to clone the PoC-Library onto a Linux machine machine with SSH protocol:

```

cd ProjectRoot

mkdir lib

git submodule add "ssh://git@github.com:VLSI-EDA/PoC.git" lib/PoC

cd lib/PoC

git remote rename origin github

cd ../..

git add .gitmodules lib/PoC

git commit -m "Added new git submodule PoC in 'lib/PoC' (PoC-Library)."

```

## On OS X

Please see the Linux instructions.

## **On Windows**

**Note:** All Windows command line instructions are intended for **Windows PowerShell**, if not marked otherwise. So executing the following instructions in Windows Command Prompt (**cmd.exe**) won't function or result in errors! See the Requirements section on where to download or update PowerShell.

Command line instructions to clone the PoC-Library onto a Windows machine with HTTPS protocol:

```

cd <ProjectRoot>

mkdir lib | cd

git submodule add "https://github.com/VLSI-EDA/PoC.git" PoC

cd PoC

git remote rename origin github

cd ..\..

git add .gitmodules lib\PoC

git commit -m "Added new git submodule PoC in 'lib\PoC' (PoC-Library)."

```

Command line instructions to clone the PoC-Library onto a Windows machine with SSH protocol:

```

cd <ProjectRoot>

mkdir lib | cd

git submodule add "ssh://git@github.com:VLSI-EDA/PoC.git" PoC

cd PoC

git remote rename origin github

cd ..\..

git add .gitmodules lib\PoC

git commit -m "Added new git submodule PoC in 'lib\PoC' (PoC-Library)."

```

# 2.3.3 Integrating PoC into Projects

## Contents of this page

- As a Git submodule

- On Linux

- On OS X

- On Windows

## As a Git submodule

The following command line instructions will integrate PoC into a existing Git repository and register PoC as a Git submodule. Therefore a directory lib\PoC\ is created and the PoC-Library is cloned as a Git submodule into that directory.

#### On Linux

```

cd ProjectRoot

mkdir lib

cd lib

git submodule add https://github.com/VLSI-EDA/PoC.git PoC

cd PoC

git remote rename origin github

cd ../..

git add .gitmodules lib\PoC

git commit -m "Added new git submodule PoC in 'lib/PoC' (PoC-Library)."

```

## On OS X

Please see the Linux instructions.

## **On Windows**

**Note:** All Windows command line instructions are intended for **Windows PowerShell**, if not marked otherwise. So executing the following instructions in Windows Command Prompt (**cmd.exe**) won't function or result in errors! See the Requirements section on where to download or update PowerShell.

```

cd ProjectRoot

mkdir lib | cd

git submodule add https://github.com/VLSI-EDA/PoC.git PoC

cd PoC

git remote rename origin github

cd ..\..

git add .gitmodules lib\PoC

git commit -m "Added new git submodule PoC in 'lib\PoC' (PoC-Library)."

```

#### See also:

Configuring PoC on a Local System

Create PoC's VHDL Configuration Files

# 2.3.4 Configuring PoC's Infrastructure

To explore PoC's full potential, it's required to configure some paths and synthesis or simulation tool chains. It's possible to relaunch the process at any time, for example to register new tools or to update tool versions.

#### Contents of this page

- Overview

- The PoC-Library

- Git

- Aldec

- Active-HDL

- Altera

- Quartus

- ModelSim Altera Edition

- Lattice

- Diamond

- Active-HDL Lattice Edition

- Mentor Graphics

- QuestaSim

- Xilinx

- ISE

- Vivado

- GHDL

- GTKWave

- Hook Files

#### Overview

The setup process is started by invoking PoC's frontend script with the command configure. Please follow the instructions on screen. Use the keyboard buttons: Y to accept, N to decline, P to skip/pass a step and Return to accept a default value displayed in brackets.

Optionally, a vendor or tool chain name can be passed to the configuration process to launch only its configuration routines.

#### On Linux:

```

cd ProjectRoot

./lib/PoC/poc.sh configure

# with tool chain name

./lib/PoC/poc.sh configure Xilinx.Vivado

```

## On OS X

Please see the Linux instructions.

#### On Windows

**Note:** All Windows command line instructions are intended for **Windows PowerShell**, if not marked otherwise. So executing the following instructions in Windows Command Prompt (**cmd.exe**) won't function or result in errors! See the Requirements section on where to download or update PowerShell.

```

cd ProjectRoot

.\lib\PoC\poc.ps1 configure

# with tool chain name

.\lib\PoC\poc.ps1 configure Xilinx.Vivado

```

#### **Introduction screen:**

```

PS D:\git\PoC> .\poc.ps1 configure

The PoC-Library - Service Tool

Explanation of abbreviations:

Y - yes P - pass (jump to next question)

N - no Ctrl + C - abort (no changes are saved)

Upper case or value in '[...]' means default value

Configuring PoC

PoC version: v1.0.1 (found in git)

Installation directory: D:\git\PoC (found in environment variable)

```

## The PoC-Library

PoC itself has a fully automated configuration routine. It detects if PoC is under Git control. If so, it extracts the current version number from the latest Git tag. The installation directory is infered from \$PoCRootDirectory setup by PoC.ps1 or poc.sh.

```

Configuring PoC

PoC version: v1.0.1 (found in git)

Installation directory: D:\git\PoC (found in environment variable)

```

#### Git

**Note:** Setting up Git and Git developer settings, is an advanced feature recommended for all developers interrested in providing Git pull requests or patches.

```

Configuring Git

Git installation directory [C:\Program Files\Git]:

Install Git mechanisms for PoC developers? [y/N/p]: y

Install Git filters? [Y/n/p]:

Installing Git filters...

Install Git hooks? [Y/n/p]:

```

```

Installing Git hooks...

Setting 'pre-commit' hook for PoC...

```

#### **Aldec**

Configure the installation directory for all Aldec tools.

```

Configuring Aldec

Are Aldec products installed on your system? [Y/n/p]: Y

Aldec installation directory [C:\Aldec]:

```

#### **Active-HDL**

```

Configuring Aldec Active-HDL

Is Aldec Active-HDL installed on your system? [Y/n/p]: Y

Aldec Active-HDL version [10.3]:

Aldec Active-HDL installation directory [C:\Aldec\Active-HDL]: C:\Aldec\Active-HDL+Student-Edit

```

#### **Altera**

Configure the installation directory for all Altera tools.

```

Configuring Altera

Are Altera products installed on your system? [Y/n/p]: Y

Altera installation directory [C:\Altera]:

```

#### Quartus

```

Configuring Altera Quartus

Is Altera Quartus-II or Quartus Prime installed on your system? [Y/n/p]: Y

Altera Quartus version [15.1]: 16.0

Altera Quartus installation directory [C:\Altera\16.0\quartus]:

```

#### **ModelSim Altera Edition**

```

Configuring ModelSim Altera Edition

Is ModelSim Altera Edition installed on your system? [Y/n/p]: Y

ModelSim Altera Edition installation directory [C:\Altera\15.0\modelsim_ae]: C:\Altera\16.0\modelsim_ae

```

#### Lattice

Configure the installation directory for all Lattice Semiconductor tools.

```

Configuring Lattice

Are Lattice products installed on your system? [Y/n/p]: Y

Lattice installation directory [D:\Lattice]:

```

#### **Diamond**

```

Configuring Lattice Diamond

Is Lattice Diamond installed on your system? [Y/n/p]: >

Lattice Diamond version [3.7]:

Lattice Diamond installation directory [D:\Lattice\Diamond\3.7_x64]:

```

#### **Active-HDL Lattice Edition**

```

Configuring Active-HDL Lattice Edition

Is Aldec Active-HDL installed on your system? [Y/n/p]: Y

Active-HDL Lattice Edition version [10.2]:

Active-HDL Lattice Edition installation directory [D:\Lattice\Diamond\3.7_x64\active-hdl]:

```

## **Mentor Graphics**

Configure the installation directory for all mentor Graphics tools.

```

Configuring Mentor

Are Mentor products installed on your system? [Y/n/p]: Y

Mentor installation directory [C:\Mentor]:

```

#### QuestaSim

```

Configuring Mentor QuestaSim

Is Mentor QuestaSim installed on your system? [Y/n/p]: Y

Mentor QuestaSim version [10.4d]: 10.4c

Mentor QuestaSim installation directory [C:\Mentor\QuestaSim\10.4c]: C:\Mentor\QuestaSim64\10.4

```

#### **Xilinx**

Configure the installation directory for all Xilinx tools.

```

Configuring Xilinx

Are Xilinx products installed on your system? [Y/n/p]: Y

Xilinx installation directory [C:\Xilinx]:

```

#### **ISE**

If an Xilinx ISE environment is available and shall be configured in PoC, then answer the following questions:

```

Configuring Xilinx ISE

Is Xilinx ISE installed on your system? [Y/n/p]: Y

Xilinx ISE installation directory [C:\Xilinx\14.7\ISE_DS]:

```

## Vivado

If an Xilinx ISE environment is available and shall be configured in PoC, then answer the following questions:

```

Configuring Xilinx Vivado

Is Xilinx Vivado installed on your system? [Y/n/p]: Y

Xilinx Vivado version [2016.2]:

Xilinx Vivado installation directory [C:\Xilinx\Vivado\2016.2]:

```

## **GHDL**

```

Configuring GHDL

Is GHDL installed on your system? [Y/n/p]: Y

GHDL installation directory [C:\Tools\GHDL\0.34dev]:

```

## **GTKWave**

```

Configuring GTKWave

Is GTKWave installed on your system? [Y/n/p]: Y

GTKWave installation directory [C:\Tools\GTKWave\3.3.71]:

```

#### **Hook Files**

PoC's wrapper scripts can be customized through pre- and post-hook file. See Wrapper Script Hook Files for more details.

# 2.3.5 Creating my\_config/my\_project.vhdl

The PoC-Library needs two VHDL files for it's configuration. These files are used to determine the most suitable implementation depending on the provided platform information. These files are also used to select appropriate work arounds.

## Create my\_config.vhdl

The my\_config.vhdl file can easily be created from the template file my\_config.vhdl.template provided by PoC in PoCRoot\src\common. (View source on GitHub.) Copy this file into the projects source directory and renamed into my\_config.vhdl.

This file should be included into version control systems and shared with other systems. my\_config.vhdl defines three global constants, which need to be adjusted:

```

constant MY_BOARD : string := "CHANGE THIS"; -- e.g. Custom, ML505, KC705, Atlys

constant MY_DEVICE : string := "CHANGE THIS"; -- e.g. None, XC5VLX50T-1FF1136, EP2$GX90FF1508C3

constant MY_VERBOSE : boolean := FALSE; -- activate report statements in VHDL subprograms

```

The easiest way is to define a board name and set MY\_DEVICE to None. So the device name is inferred from the board information stored in PoCRoot\src\common\board.vhdl. If the requested board is not known to PoC or it's custom made, then set MY BOARD to Custom and MY DEVICE to the full FPGA device string.

## Example 1: A "Stratix II GX Audio Video Development Kit" board:

```

constant MY_BOARD : string := "S2GXAV"; -- Stratix II GX Audio Video Development Kit

constant MY_DEVICE : string := "None"; -- infer from MY_BOARD

```

#### Example 2: A custom made Spartan-6 LX45 board:

```

constant MY_BOARD : string := "Custom";

constant MY_DEVICE : string := "XC6SLX45-3CSG324";

```

## Create my\_project.vhdl

The my\_project.vhdl file can also be created from a template file my\_project.vhdl.template provided by PoC in PoCRoot\src\common.

The file should to be copyed into a projects source directory and renamed into my\_project.vhdl. This file **must not** be included into version control systems – it's private to a computer. my\_project.vhdl defines two global constants, which need to be adjusted:

```

constant MY_PROJECT_DIR : string := "CHANGE THIS"; -- e.g. "d:/vhdl/myproject/",

constant MY_OPERATING_SYSTEM : string := "CHANGE THIS"; -- e.g. "WINDOWS", "LINUX"

```

"/home/me/p

#### **Example 1: A Windows System:**

```

constant MY_PROJECT_DIR : string := "D:/git/GitHub/PoC/";

constant MY_OPERATING_SYSTEM : string := "WINDOWS";

```

## **Example 2: A Debian System:**

```

constant MY_PROJECT_DIR : string := "/home/paebbels/git/GitHub/PoC/";

constant MY_OPERATING_SYSTEM : string := "LINUX";

```

#### See also:

Running one or more testbenches The installation can be checked by running one or more of PoC's testbenches.

**Running one or more netlist generation flows** The installation can also be checked by running one or more of PoC's synthesis flows.

# 2.3.6 Adding IP Cores to a Project

## **Manually Addind IP Cores**

## **Adding IP Cores to Altera Quartus**

#### **Todo**

No documentation available.

#### **Adding IP Cores to Lattice Diamond**

#### Todo

No documentation available.

## **Adding IP Cores to Xilinx ISE**

## Todo

No documentation available.

## **Adding IP Cores to Xilinx Vivado**

## Todo

No documentation available.

## 2.3.7 Simulation

## Contents of this Page

- Overview

- Quick Example

- Vendor Specific Testbenches

- Running a Single Testbench

- Aldec Active-HDL

- Cocotb with QuestaSim backend

- GHDL (plus GTKwave)

- Mentor Graphics OuestaSim

- Xilinx ISE Simulator

- Xilinx Vivado Simulator

- Running a Group of Testbenches

- Continuous Integration (CI)

#### Overview

The Python Infrastructure shipped with the PoC-Library can launch manual, half-automated and fully automated testbenches. The testbench can be run in command line or GUI mode. If available, the used simulator is launched with pre-configured waveform files. This can be done by invoking one of PoC's frontend script:

- poc.sh: poc.sh <common options> <simulator> <module> <simulator options> Use this fronend script on Darwin, Linux and Unix platforms.

- poc.ps1: poc.ps1 <common options> <simulator> <module> <simulator options> Use this frontend script Windows platforms.

**Attention:** All Windows command line instructions are intended for Windows PowerShell, if not marked otherwise. So executing the following instructions in Windows Command Prompt (cmd.exe) won't function or result in errors!

## See also:

**PoC Configuration** See the Configuration page on how to configure PoC and your installed simulator tool chains. This is required to invoke the simulators.

**Supported Simulators** See the Intruction page for a list of supported simulators.

# **Quick Example**

The following quick example uses the GHDL Simulator to analyze, elaborate and simulate a testbench for the module <code>arith\_prng</code> (Pseudo Random Number Generator - PRNG). The VHDL file <code>arith\_prng.vhdl</code> is located at <code>PoCRoot\src\arith</code> and virtually a member in the <code>PoC.arith</code> namespace. So the module can be identified by an unique name: <code>PoC.arith.prng</code>, which is passed to the frontend script.

## Example 1:

```

cd PoCRoot

.\poc.ps1 ghdl PoC.arith.prng

```

The CLI command ghdl chooses *GHDL Simulator* as the simulator and passes the fully qualified PoC entity name PoC.arith.prng as a parameter to the tool. All required source file are gathered and compiled to an executable. Afterwards this executable is launched in CLI mode and it's outputs are displayed in console:

Each testbench uses PoC's simulation helper packages to count asserts and to track active stimuli and checker processes. After a completed simulation run, an report is written to STDOUT or the simulator's console. Note the line SIMULATION RESULT = PASSED. For each simulated PoC entity, a line in the overall report is created. It lists the runtime per testbench and the simulation status (... ERROR, FAILED, NO ASSERTS or PASSED).

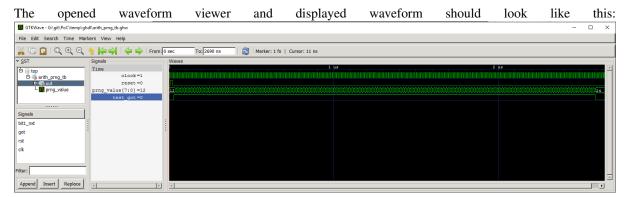

## Example 2:

Passing an additional option --gui to the service tool, opens the testbench in GUI-mode. If a waveform configuration file is present (e.g. a \*.gtkw file for GTKWave), then it is preloaded into the simulator's waveform viewer.

## **Vendor Specific Testbenches**

PoC is shipped with a set of well known FPGA development boards. This set is extended by a list of generic boards, named after each supported FPGA vendor. These generic boards can be used in simulations to select a representative FPGA of a supported device vendor. If no board or device name is passed to a testbench run, the GENERIC board is chosen.

| Board Name | Target Board | Target Device  |

|------------|--------------|----------------|

| GENERIC    | GENERIC      | GENERIC        |

| Altera     | DE4          | Stratix-IV 230 |

| Lattice    | ECP5Versa    | ECP5-45UM      |

| Xilinx     | KC705        | Kintex-7 325T  |

A vendor specific testbench can be launched by passing either --board=xxx or --device=yyy as an additional parameter to the PoC scripts.

```

# Example 1 - A Lattice board

.\poc.ps1 ghdl PoC.arith.prng --board=Lattice

# Example 2 - A Altera Stratix IV board

.\poc.ps1 ghdl PoC.arith.prng --board=DE4

# Example 3 - A Xilinx Kintex-7 325T device

.\poc.ps1 ghdl PoC.arith.prng --device=XC7K325T-2FFG900

```

**Note:** Running vendor specific testbenches may require pre-compiled vendor libraries. Some simulators are shipped with diverse pre-compiled libraries, others include scripts or user guides to pre-compile them on the target system.

PoC is shipped with a set of pre-compile scripts to offer a unified interface and common storage for all supported vendor's pre-compile procedures. See Pre-Compiling Vendor Libraries.

## **Running a Single Testbench**

A testbench run is supervised by PoC's PoCRoot\py\PoC.py service tool, which offers a consistent interface to all simulators. Unfortunately, every platform has it's specialties, so a wrapper script is needed as abstraction from the host's operating system. Depending on the choosen tool chain, the wrapper script will source or invoke the vendor tool's environment scripts to pre-load the needed environment variables, paths or license file settings.

The order of options to the frontend script is as following: <common options> <simulator> <module> <simulator options>

The frontend offers several common options:

| Common Option |          | Description                   |

|---------------|----------|-------------------------------|

| -q            | –quiet   | Quiet-mode (print nothing)    |

| -v            | -verbose | Print more messages           |

| -d            | -debug   | Debug mode (print everything) |

|               | –dryrun  | Run in dry-run mode           |

One of the following supported simulators can be choosen, if installed and configured in PoC:

| Simulator | Description                                 |

|-----------|---------------------------------------------|

| asim      | Active-HDL Simulator                        |

| cocotb    | Cocotb simulation using QuestaSim Simulator |

| ghdl      | GHDL Simulator                              |

| isim      | Xilinx ISE Simulator                        |

| vsim      | QuestaSim Simulator or ModelSim             |

| xsim      | Xilinx Vivado Simulator                     |

A testbench run can be interrupted by sending a keyboard interrupt to Python. On most operating systems this is done by pressing Ctrl + C. If PoC runs multiple testbenches at once, all finished testbenches are reported with there testbench result. The aborted testbench will be listed as errored.

## Aldec Active-HDL

The command to invoke a simulation using Active-HDL is asim followed by a list of PoC entities. The following options are supported for Active-HDL:

# The PoC-Library Documentation, Release 1.0.0

| Simulator Option |                            | Description                         |

|------------------|----------------------------|-------------------------------------|

|                  | -board= <board></board>    | Specify a target board.             |

|                  | -device= <device></device> | Specify a target device.            |

|                  | -std=[87 93 02 08]         | Select a VHDL standard. Default: 08 |

Note: GUI mode for Active-HDL is not yet supported.

## **Example:**

```

cd PoCRoot

.\poc.ps1 asim PoC.arith.prng --std=93

```

#### Cocotb with QuestaSim backend

The command to invoke a Cocotb simulation using QuestaSim is cocotb followed by a list of PoC entities. The following options are supported for Cocotb:

| Simulator Option |                            | Description                                |

|------------------|----------------------------|--------------------------------------------|

|                  | -board= <board></board>    | Specify a target board.                    |

|                  | -device= <device></device> | Specify a target device.                   |

| -g               | -gui                       | Start the simulation in the QuestaSim GUI. |

**Note:** Cocotb is currently only on Linux with QuestaSim supported. We are working to support the Windows platform and the GHDL backend.

## Example:

```

cd PoCRoot

.\poc.ps1 cocotb PoC.cache.par

```

## **GHDL** (plus GTKwave)

The command to invoke a simulation using GHDL is ghdl followed by a list of PoC entities. The following options are supported for GHDL:

| Simulator Option |                            | Description                                             |

|------------------|----------------------------|---------------------------------------------------------|

|                  | -board= <board></board>    | Specify a target board.                                 |

|                  | -device= <device></device> | Specify a target device.                                |

| -g               | –gui                       | Start GTKwave, if installed. Open *.gtkw, if available. |

|                  | -std=[87 93 02 08]         | Select a VHDL standard. Default: 08                     |

## Example:

```

cd PoCRoot

.\poc.ps1 ghdl PoC.arith.prng --board=Atlys -g

```

#### **Mentor Graphics QuestaSim**

The command to invoke a simulation using QuestaSim or ModelSim is vsim followed by a list of PoC entities. The following options are supported for QuestaSim:

| Simulator Option |                            | Description                                |

|------------------|----------------------------|--------------------------------------------|

|                  | -board= <board></board>    | Specify a target board.                    |

|                  | -device= <device></device> | Specify a target device.                   |

| -g               | -gui                       | Start the simulation in the QuestaSim GUI. |

|                  | -std=[87 93 02 08]         | Select a VHDL standard. Default: 08        |

#### **Example:**

```

cd PoCRoot

.\poc.ps1 vsim PoC.arith.prng --board=DE4 --gui

```

#### Xilinx ISE Simulator

The command to invoke a simulation using ISE Simulator (isim) is isim followed by a list of PoC entities. The following options are supported for ISE Simulator:

| Simulator Option |                            | Description                                           |

|------------------|----------------------------|-------------------------------------------------------|

|                  | -board= <board></board>    | Specify a target board.                               |

|                  | -device= <device></device> | Specify a target device.                              |

| -g               | –gui                       | Start the simulation in the ISE Simulator GUI (iSim). |

#### **Example:**

```

cd PoCRoot

.\poc.ps1 isim PoC.arith.prng --board=Atlys -g

```

#### Xilinx Vivado Simulator

The command to invoke a simulation using Vivado Simulator (isim) is xsim followed by a list of PoC entities. The following options are supported for Vivado Simulator:

| Simulator Option |                            | Description                         |

|------------------|----------------------------|-------------------------------------|

|                  | -board= <board></board>    | Specify a target board.             |

|                  | -device= <device></device> | Specify a target device.            |

| -g               | -gui                       | Start Vivado in simulation mode.    |

|                  | -std=[93 08]               | Select a VHDL standard. Default: 93 |

#### **Example:**

```

cd PoCRoot

.\poc.ps1 xsim PoC.arith.prng --board=Atlys -g

```

## **Running a Group of Testbenches**

Each simulator can be invoked with a space seperated list of PoC entiries or a wildcard at the end of the fully qualified entity name.

Supported wildcard patterns are  $\star$  and ?. Question mark refers to all entities in a PoC (sub-)namespace. Asterisk refers to all PoC entiries in the current namespace and all sub-namespaces.

## **Examples for testbenches groups:**

| PoC entity list        | Description                                          |

|------------------------|------------------------------------------------------|

| PoC.arith.prng         | A single PoC entity: arith_prng                      |

| PoC.*                  | All entities in the whole library                    |

| PoC.io.ddrio.?         | All entities in PoC.io.ddrio: ddrio_in, ddrio_inout, |

|                        | ddrio_out                                            |

| PoC.fifo.* PoC.cache.* | All FIFO, cache and data-structure testbenches.      |

| PoC.dstruct.*          |                                                      |

```

cd PoCRoot

.\poc.ps1 -q asim PoC.arith.prng PoC.io.ddrio.* PoC.sort.lru_cache

```

Resulting output: PS G:\git\PoC>

## **Continuous Integration (CI)**

All PoC testbenches are executed on every GitHub upload (push) via Travis-CI. The testsuite runs all testbenches for the virtual board <code>GENERIC</code> with an FPGA device called <code>GENERIC</code>. We can't run vendor dependent testbenches, because we can't upload the vendor simulation libraries to Travis-CI.

To reproduce the Travis-CI results on a local machine, run the following command. The -q option, launches the frontend in quiet mode to reduce the command line messages:

```

cd PoCRoot

.\poc.ps1 -q ghdl PoC.*

```

```

Windows PowerShell

×

Testbench: PoC.sort.sortnet.OddEvenMergeSort

Testbench: PoC.sort.sortnet.Stream_Adapter

Testbench: PoC.sort.sortnet.Stream_Adapter

Testbench: PoC.sort.sortnet.Stream_Adapter2

Testbench: PoC.sort.lru_cache

| Time |

Status

addw

convert_bin2bcd

counter_bcd

PASSED

0:04

0:01

0:02

0:03

0:02

0:01

0:01

0:01

PASSED

PASSED

PASSED

PASSED

PASSED

PASSED

firstone

prefix_and

prefix_or

0:02

0:02

PASSED

PASSED

0:02

0:02

0:02

0:02

ddrio

0:01

0:01

0:01

in

inout

PASSED

PASSED

out

uart

rx

Debounce

PASSED

PASSED

0:02

0:02

m

lut

Sine

0:01

NO ASSERTS

0:01

sdp

gearbox

NO ASSERTS

NO ASSERTS

0:02

0:01

PASSED

NO ASSERTS

PASSED

PASSED

0:02

0:04

Average

Histogram

Minimum

0:01

0:01

0:02

sortnet

BitonicSort

0:56

2:54

0:46

0:03

OddEvenSort

OddEvenMergeSort

Stream_Adapter

Stream_Adapter2

lru_cache

ime: 9:07 Count: 41

Passed: 30 No Asserts: 9 Failed: 2 Errors: 0

S G:\git\PoC>

```

If the vendor libraries are available and pre-compiled, then it's also possible to run a CI flow for a specific vendor. This is an Altera example for the Terrasic DE4 board:

```

cd PoCRoot

.\poc.ps1 -q vsim PoC.* --board=DE4

```

#### See also:

**PoC Configuration** See the Configuration page on how to configure PoC and your installed simulator tool chains. This is required to invoke the simulators.

Latest Travis-CI Report Browse the list of branches at Travis-CI.org.

# 2.3.8 Synthesis

## Contents of this Page

- Overview

- Quick Example

- Running a single Synthesis

- Altera Quartus

- Lattice Diamond

- Xilinx ISE Synthesis Tool (XST)

- Xilinx ISE Core Generator

- Xilinx Vivado Synthesis

#### Overview

The Python infrastructure shipped with the PoC-Library can launch manual, half-automated and fully automated synthesis runs. This can be done by invoking one of PoC's frontend script:

- poc.sh: poc.sh <common options> <compiler> <module> <compiler options> Use this fronend script on Darwin, Linux and Unix platforms.

- **poc.ps1:** poc.ps1 <common options> <compiler> <module> <compiler options> Use this frontend script Windows platforms.

**Attention:** All Windows command line instructions are intended for Windows PowerShell, if not marked otherwise. So executing the following instructions in Windows Command Prompt (cmd.exe) won't function or result in errors!

#### See also:

**PoC Configuration** See the Configuration page on how to configure PoC and your installed synthesis tool chains. This is required to invoke the compilers.

**Supported Compiler** See the Intruction page for a list of supported compilers.

#### See also:

List of Supported FPGA Devices See this list to find a supported and well known target device.

List of Supported Development Boards See this list to find a supported and well known development board.

## **Quick Example**

The following quick example uses the Xilinx Systesis Tool (XST) to synthesize a netlist for IP core arith\_prng (Pseudo Random Number Generator - PRNG). The VHDL file arith\_prng.vhdl is located at PoCRoot\src\arith and virtually a member in the *PoC.arith* namespace. So the module can be identified by an unique name: PoC.arith.prng, which is passed to the frontend script.

## Example 1:

```

cd PoCRoot

.\poc.ps1 xst PoC.arith.prng --board=KC705

```

The CLI command xst chooses *Xilinx Synthesis Tool* as the synthesizer and passes the fully qualified PoC entity name PoC.arith.prng as a parameter to the tool. Additionally, the development board name is required to load the correct my\_config.vhdl file. All required source file are gathered and synthesized to a netlist.

# Running a single Synthesis

A synthesis run is supervised by PoC's PoCRoot\py\PoC.py service tool, which offers a consistent interface to all synthesizers. Unfortunately, every platform has it's specialties, so a wrapper script is needed as abstraction from the host's operating system. Depending on the choosen tool chain, the wrapper script will source or invoke the vendor tool's environment scripts to pre-load the needed environment variables, paths or license file settings.

The order of options to the frontend script is as following: <common options> <compiler> <module> <compiler options>

The frontend offers several common options:

| Common Option |          | Description                   |

|---------------|----------|-------------------------------|

| -q            | –quiet   | Quiet-mode (print nothing)    |

| -v            | -verbose | Print more messages           |

| -d            | -debug   | Debug mode (print everything) |

|               | –dryrun  | Run in dry-run mode           |

One of the following supported synthesizers can be choosen, if installed and configured in PoC:

| Simulator | Description                                      |

|-----------|--------------------------------------------------|

| quartus   | Altera Quartus II or Quartus Prime               |

| lse       | Lattice Diamond - Lattice Synthesis Engine (LSE) |

| xst       | Xilinx ISE Systhesis Tool (XST)                  |

| coregen   | Xilinx ISE Core Generator (CoreGen)              |

| vivado    | Xilinx Vivado Synthesis                          |

### **Altera Quartus**

The command to invoke a synthesis using Altera Quartus II or Quartus Prime is quartus followed by a list of PoC entities. The following options are supported for Quartus:

| Simulator Option           | Description              |

|----------------------------|--------------------------|

| -board= <board></board>    | Specify a target board.  |

| -device= <device></device> | Specify a target device. |

2.3. Using PoC 33

#### **Example:**

```

cd PoCRoot

.\poc.ps1 quartus PoC.arith.prng --board=DE4

```

#### **Lattice Diamond**

The command to invoke a synthesis using Altera Quartus II or Quartus Prime is quartus followed by a list of PoC entities. The following options are supported for Quartus:

| Simulator Option                                                          |         | Description              |

|---------------------------------------------------------------------------|---------|--------------------------|

| -board= <e< td=""><td>BOARD&gt;</td><td>Specify a target board.</td></e<> | BOARD>  | Specify a target board.  |

| -device=<                                                                 | DEVICE> | Specify a target device. |

#### **Example:**

```

cd PoCRoot

.\poc.ps1 quartus PoC.arith.prng --board=DE4

```

## Xilinx ISE Synthesis Tool (XST)

The command to invoke a synthesis using Altera Quartus II or Quartus Prime is quartus followed by a list of PoC entities. The following options are supported for Quartus:

| Simulator Option           | Description              |

|----------------------------|--------------------------|

| -board= <board></board>    | Specify a target board.  |

| -device= <device></device> | Specify a target device. |

### **Example:**

```

cd PoCRoot

.\poc.ps1 quartus PoC.arith.prng --board=DE4

```

### Xilinx ISE Core Generator

The command to invoke a synthesis using Altera Quartus II or Quartus Prime is quartus followed by a list of PoC entities. The following options are supported for Quartus:

| Simulator Option           | Description              |

|----------------------------|--------------------------|

| -board= <board></board>    | Specify a target board.  |

| -device= <device></device> | Specify a target device. |

#### **Example:**

```

cd PoCRoot

.\poc.ps1 quartus PoC.arith.prng --board=DE4

```

## Xilinx Vivado Synthesis

The command to invoke a synthesis using Altera Quartus II or Quartus Prime is quartus followed by a list of PoC entities. The following options are supported for Quartus:

| Simulator Option           | Description              |

|----------------------------|--------------------------|

| -board= <board></board>    | Specify a target board.  |

| -device= <device></device> | Specify a target device. |

#### **Example:**

```

cd PoCRoot

.\poc.ps1 quartus PoC.arith.prng --board=DE4

```

# 2.3.9 Project Management

Overview

**Solutions**

**Projects**

# 2.3.10 Pre-Compiling Vendor Libraries

# Contents of this Page

- Overview

- Supported Simulators

- FPGA Vendor's Primitive Libraries

- Altera

- \* On Linux

- \* On Windows

- Lattice

- \* On Linux

- \* On Windows

- Xilinx ISE

- \* On Linux

- \* On Windows

- Xilinx Vivado

- \* On Linux

- \* On Windows

- Third-Party Libraries

- OSVVM

- \* On Linux

- \* On Windows

- Simulator Adapters

- Cocotb

- \* On Linux

- \* On Windows

# Overview

Running vendor specific testbenches may require pre-compiled vendor libraries. Some vendors ship their simulators with diverse pre-compiled libraries, but these don't include primitive libraries from hardware vendors. More

2.3. Using PoC 35

over, many auxillary libraries are outdated. Hardware vendors ship their tool chains with pre-compile scripts or user guides to pre-compile the primitive libraries for a list of supported simulators on a target system.

PoC is shipped with a set of pre-compile scripts to offer a unified interface and common storage for all supported vendor's pre-compile procedures. The scripts are located in \tools\precompile\ and the output is stored in \temp\precompiled\<Simulator>\<Library>.

# **Supported Simulators**

The current set of pre-compile scripts support these simulators:

| Vendor      | Simulator and     | Altera          | Lattice         | Xilinx (ISE)     | Xilinx (Vivado) |

|-------------|-------------------|-----------------|-----------------|------------------|-----------------|

|             | Edition           |                 |                 |                  |                 |

| 20 Cincold  | GHDL with         | yes yes         | yes yes         | yes yes          | yes yes         |

| 20. Gingold | std=93c           |                 |                 |                  |                 |

|             | GHDL with         |                 |                 |                  |                 |

|             | std=08            |                 |                 |                  |                 |

| Aldec       | Active-HDL        | planned planned | planned shipped | planned planned  | planned planned |

|             | Active-HDL        | planned         | planned         | planned          | planned         |

|             | Lattice Ed.       |                 |                 |                  |                 |

|             | Reviera-PRO       |                 |                 |                  |                 |

| Mentor      | ModelSim Mod-     | yes shipped yes | yes yes yes     | yes yes yes      | yes yes yes     |

|             | elSim Altera Ed.  |                 |                 |                  |                 |

|             | QuestaSim         |                 |                 |                  |                 |

| Xilinx      | ISE Simulator Vi- |                 |                 | shipped not sup- | not supported   |

|             | vado Simulator    |                 |                 | ported           | shipped         |

## **FPGA Vendor's Primitive Libraries**

## Altera

**Note:** The Altera Quartus tool chain needs to be configured in PoC. See Configuring PoC's Infrastruture for further details.

### On Linux

```

# Example 1 - Compile for all Simulators

./tools/precompile/compile-altera.sh --all

# Example 2 - Compile only for GHDL and VHDL-2008

./tools/precompile/compile-altera.sh --ghdl --vhdl2008

```

# List of command line arguments:

| Common Option |           | Description                 |

|---------------|-----------|-----------------------------|

| -h            | –help     | Print embedded help page(s) |

| -c            | –clean    | Clean-up directories        |

| -a            | –all      | Compile for all simulators  |

|               | -ghdl     | Compile for GHDL            |

|               | –questa   | Compile for QuestaSim       |

|               | -vhdl93   | Compile only for VHDL-93    |

|               | -vhd12008 | Compile only for VHDL-2008  |

### On Windows

```

# Example 1 - Compile for all Simulators

.\tools\precompile\compile-altera.ps1 -All

# Example 2 - Compile only for GHDL and VHDL-2008

.\tools\precompile\compile-altera.ps1 -GHDL -VHDL2008

```

#### List of command line arguments:

| Common Option |           | Description                 |

|---------------|-----------|-----------------------------|

| -h            | -Help     | Print embedded help page(s) |

| -c            | -Clean    | Clean-up directories        |

| -a            | -All      | Compile for all simulators  |

|               | -GHDL     | Compile for GHDL            |

|               | -Questa   | Compile for QuestaSim       |

|               | -VHDL93   | Compile only for VHDL-93    |

|               | -VHDL2008 | Compile only for VHDL-2008  |

#### Lattice

**Note:** The Lattice Diamond tool chain needs to be configured in PoC. See Configuring PoC's Infrastruture for further details.

## On Linux

```

# Example 1 - Compile for all Simulators

./tools/precompile/compile-lattice.sh --all

# Example 2 - Compile only for GHDL and VHDL-2008

./tools/precompile/compile-lattice.sh --ghdl --vhdl2008

```

#### List of command line arguments:

| Common Option |           | Description                 |

|---------------|-----------|-----------------------------|

| -h            | –help     | Print embedded help page(s) |

| -c            | –clean    | Clean-up directories        |

| -a            | –all      | Compile for all simulators  |

|               | -ghdl     | Compile for GHDL            |

|               | –questa   | Compile for QuestaSim       |

|               | -vhdl93   | Compile only for VHDL-93    |

|               | -vhdl2008 | Compile only for VHDL-2008  |

### On Windows

```

# Example 1 - Compile for all Simulators

.\tools\precompile\compile-lattice.ps1 -All

# Example 2 - Compile only for GHDL and VHDL-2008

.\tools\precompile\compile-lattice.ps1 -GHDL -VHDL2008

```

# List of command line arguments:

| Common Option |           | Description                 |

|---------------|-----------|-----------------------------|

| -h            | -Help     | Print embedded help page(s) |

| -c            | -Clean    | Clean-up directories        |

| -a            | -All      | Compile for all simulators  |

|               | -GHDL     | Compile for GHDL            |

|               | -Questa   | Compile for QuestaSim       |

|               | -VHDL93   | Compile only for VHDL-93    |

|               | -VHDL2008 | Compile only for VHDL-2008  |

2.3. Using PoC 37

#### Xilinx ISE

**Note:** The Xilinx ISE tool chain needs to be configured in PoC. See Configuring PoC's Infrastruture for further details.

#### On Linux

```

# Example 1 - Compile for all Simulators

./tools/precompile/compile-xilinx-ise.sh --all

# Example 2 - Compile only for GHDL and VHDL-2008

./tools/precompile/compile-xilinx-ise.sh --ghdl --vhdl2008

```

#### List of command line arguments:

| Common Option |           | Description                 |  |

|---------------|-----------|-----------------------------|--|

| -h            | –help     | Print embedded help page(s) |  |

| -c            | –clean    | Clean-up directories        |  |

| -a            | –all      | Compile for all simulators  |  |

|               | -ghdl     | Compile for GHDL            |  |

|               | –questa   | Compile for QuestaSim       |  |

|               | -vhdl93   | Compile only for VHDL-93    |  |

|               | -vhd12008 | Compile only for VHDL-2008  |  |

## On Windows

```

# Example 1 - Compile for all Simulators

.\tools\precompile\compile-xilinx-ise.ps1 -All

# Example 2 - Compile only for GHDL and VHDL-2008

.\tools\precompile\compile-xilinx-ise.ps1 -GHDL -VHDL2008

```

## List of command line arguments:

| Common Option |           | Description                 |

|---------------|-----------|-----------------------------|

| -h            | -Help     | Print embedded help page(s) |

| -c            | -Clean    | Clean-up directories        |

| -a            | -All      | Compile for all simulators  |

|               | -GHDL     | Compile for GHDL            |

|               | -Questa   | Compile for QuestaSim       |

|               | -VHDL93   | Compile only for VHDL-93    |

|               | -VHDL2008 | Compile only for VHDL-2008  |

# Xilinx Vivado

**Note:** The Xilinx Vivado tool chain needs to be configured in PoC. See Configuring PoC's Infrastruture for further details.

#### On Linux

```

# Example 1 - Compile for all Simulators

./tools/precompile/compile-xilinx-vivado.sh --all

# Example 2 - Compile only for GHDL and VHDL-2008

./tools/precompile/compile-xilinx-vivado.sh --ghdl --vhdl2008

```

### List of command line arguments:

| Common Option |           | Description                 |  |