# eZ80 Heaven

Release 1.0

**KingInfinity and HactarCE**

Apr 01, 2017

# Tutorials

| 1  | Introduction to Assembly         1.1       What is assembly?         1.2       Setting up                                                                  | <b>3</b><br>3<br>3                                                                 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2  | Program Structure                                                                                                                                          | 7                                                                                  |

| 3  | Hex, Binary, and Decimal                                                                                                                                   | 9                                                                                  |

| 4  | Registers and Indirection         4.1       The Registers         4.2       Addresses         4.3       Indirection                                        | <b>13</b><br>13<br>14<br>14                                                        |

| 5  | Labels                                                                                                                                                     | 15                                                                                 |

| 6  | Romcalls                                                                                                                                                   | 17                                                                                 |

| 7  | Hooks                                                                                                                                                      | 19                                                                                 |

| 8  | Arithmetic Instructions         8.1       ADC         8.2       ADD         8.3       CP         8.4       DAA         8.5       DEC         8.6       INC | <ul> <li>21</li> <li>22</li> <li>23</li> <li>24</li> <li>25</li> <li>25</li> </ul> |

| 9  | Bit Manipulation           9.1         BIT           9.2         RES           9.3         SET                                                             | 27<br>27<br>29<br>31                                                               |

| 10 | Bit Shifts           10.1         RL                                                                                                                       | <b>35</b><br>35                                                                    |

|    | 10.1       RL         10.2       RLA         10.3       RLC         10.4       RLCA                                                                        | 36<br>37<br>38                                                                     |

|    | 10.5 RLD                                                                                                                                                   | 39                                                                                 |

| 11 | 10.6       RR         10.7       RRA         10.8       RRC         10.9       RRCA         10.10       RD         10.11       SLA         10.12       SRA         10.13       SRL         11.1       CPD | <ul> <li>39</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> <li>45</li> <li>46</li> <li>49</li> <li>49</li> </ul> |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|    | 11.2       CPDR         11.3       CPI         11.4       CPIR         11.5       LDD         11.6       LDDR         11.7       LDI         11.8       LDIR                                              | 49<br>50<br>51<br>52<br>52<br>53<br>54                                                                                             |

| 12 | ю                                                                                                                                                                                                         | 57                                                                                                                                 |

| 13 | Load And Exchange                                                                                                                                                                                         | 59                                                                                                                                 |

| 14 | Logic                                                                                                                                                                                                     | 61                                                                                                                                 |

| 15 | Program Flow                                                                                                                                                                                              | 63                                                                                                                                 |

| 16 | Processor Control                                                                                                                                                                                         | 65                                                                                                                                 |

| 17 | Hexcodes         17.1       What are hex codes?         17.2       General         17.3       LCD         17.4       Run Indicator                                                                        | <b>67</b><br>67<br>68<br>69                                                                                                        |

|    |                                                                                                                                                                                                           |                                                                                                                                    |

Contents:

## Introduction to Assembly

You want more games for your shiny new TI-84+CE? Why don't you make them yourself?

## What is assembly?

Assembly is a very powerful language that you can use on your TI-84+CE! When you write in assembly, you write in a human readable form of machine code, which allows you to create quicker programs that can access and do more than TI-BASIC. Mistakes in assembly can be messier than in TI-BASIC- but usually only as severe as a ram clear, so before you start this guide, back up your calculator to prevent any data loss!

## Setting up

## What you'll need

### A program editor

To write your program, you can use almost any text editor. We prefer Notepad++, as it is really easy to use for beginners and it has some nice features for developing.

Download Here: Notepad++ Syntax Highlighting: Notepad++ eZ80 Syntax Highlighting

#### An assembler

An assembler lets you take the code you have created and make it into a program that the TI-84 Plus CE can use. We recommend SPASM-ng when coding in eZ80.

Download Here: Spasm-ng

#### A debugger/emulator or a TI-84+CE

A debugger is useful for seeing what your code does and finding errors. Unfortunately, at the time of this writing, the only 84+CE emulator available for download is CEmu, which is hardly in a usable state. Because of this, we need TI's Connect software to transfer our programs to our calculator, and we'll also need a link cable (which should have come with your calculator) and the calculator itself.

Download Here: TI Connect CE

#### **TI 84+CE Equates File**

This file tells your program and the compiler where things are located on your calculator.

Download Here: ti84pce.inc

### Setting up the assembler

Alright, now we can get to putting together all the materials we just downloaded! Create a folder and call it "My First ASM Program" (or anything else). Inside create three folders: bin, includes, and tools. Rename SPASM to just spasm.exe and put it inside the folder named tools. Put ti84pce.inc inside the includes folder.

Create a file named Example.asm in your folder. Inside this file, write the following code.

```

#include "includes\ti84pce.inc"

.assume ADL=1

.org userMem-2

.db tExtTok,tAsm84CeCmp

call _homeup

call _ClrScrnFull

ld hl,TutorialText

call _PutS

call _GetKey

call _ClrScrnFull

res donePrgm,(iy+doneFlags)

ret

TutorialText:

.db "Excellent job! :) You havecreated your first assembly program!",0

```

Don't worry; we'll revisit what all this code does later on.

Now, create a file named build.bat. Inside this file, write the following code:

@echo off

:A

tools\spasm -E -T Example.asm bin\Example.8xp

Pause

Goto A

Run build.bat by double-clicking on it. Inside the "bin" folder you should see a file named FIRSTPRGM.8xp. Transfer this onto your calculator using TI Connect CE and run it by pressing  $2nd \rightarrow Catalog$  and selecting the Asm ( token, then pressing Prgm and selecting EXAMPLE (or whatever you program was called). It should look something like this: Asm (prgmEXAMPLE

If this doesn't work, try again to make sure you followed each step of the tutorial again. You can also post for help on the Cemetech forums.

In the next lesson we'll dive right into learning assembly.

## **Program Structure**

Every program in assembly follows a specific format.

```

#include "includes\ti84pce.inc"

.assume ADL=1

.org userMem-2

.db tExtTok,tAsm84CeCmp

; Program code

ret

```

But what does all of this code do?

#include "includes\ti84pce.inc"

This is a file that includes lots of locations of routines and variables and various other things in the calculator's operating system that we can use.

.assume ADL=1

This tells the assembler to assume that ADL mode is on. ADL mode means the processor is using 24-bit register pairs and memory addresses, which is the the calculator's default.

.org userMem-2

This tells the assembler that this program will be located at userMem-2, so any memory addresses we reference should be relative to that. (The program is actually placed at userMem, but there are two bytes right after this which are removed from the program by the OS before it is placed at userMem.)

.db tExtTok, tAsm84CeCmp

This is exactly equivalent to the Asm84CEPrgm token in BASIC; it tells your calculator that it should be executing an assembly program instead of a BASIC program. This is why when you try to run an assembly program on your calculator without the Asm ( token, you get an error (and why you can't run a BASIC program with the Asm ( token).

; Program code

This is where you can actually write the program's code.

ret

This exits the program (usually). More on that later.

In the next tutorial we'll be learn about how numbers work on your calculator.

Hex, Binary, and Decimal

#### If you are already familiar with binary and hexadecimal, you may skip straight on to the next tutorial.

If you would prefer a video tutorial, you can use this instead. Just know that assembly programmers use the prefix "\$" for hexadecimal and "%" for binary.

When we humans write numbers, we like to use base 10, also called decimal. Decimal is a number system in which there are ten digits (0-9). We can write any number from zero to nine using that digit.

• 4

But if we want to write a number greater than nine, we have to use two digits.

• 42

The digit on the left tells you how many "tens" there are in this number (because we use base 10) and the digit on the right tells you how many "ones" there are in this number. So we can say that a two-digit number is equal to ( $10 \times digit$  on the left) + digit on the right.

For numbers greater than 99, the highest two-digit number, we use three digits.

• 256

The digit on the right now tells you how many "hundreds" there are (one hundred being the next power of ten), and the middle digit tells you how many "tens" there are, etc. So we can say that a three-digit number is equal to "( 100 \* digit on the left ) + ( 10 \* digit in the middle ) + digit on the right

I'm sure you can see the pattern by now.

Humans may like base 10, but computers don't. Computers can't keep track of ten digits very easily. They only like two: 0 and 1. A number system using only two digits is base 2, or binary. When we write a binary number, we usually put a percent sign % in front of it to make it clear that it isn't base 10. Here's what a typical binary number may look like: %101010

In base 10, each digit is ten times as significant as the next. For example, a small change in the "hundreds" place makes a much bigger change in the value of a number than a change in the "tens" place, and likewise between the "tens" and "ones" places. In binary, each digit is twice as significant as the one after it. What do I mean by that? Well on the far left, there's the "ones" place as we would expect it. After that comes the "twos" place. And after that comes

the "fours" place (2 \* 2 = 4). And the "eights" (4 \* 2 = 8), "sixteens" (8 \* 2 = 16), "thirty-twos," and so on. It will really pay to memorize your powers of two at least up to 2<sup>8</sup>, which is 256 (in decimal notation).

So how can we use this information to go from a binary number to a decimal number? We make a chart!

| Place | 32's | 16's | 8's | 4's | 2's | 1's |

|-------|------|------|-----|-----|-----|-----|

| Digit | 1    | 0    | 1   | 0   | 1   | 0   |

Okay, so now how do we do this? We multiply down and add across. So let's start from the right:

There is a 0 in the 1s place, so we multiply 1 times 0. The result is 0.

There is a 1 in the 2s place, so we multiply 2 times 1. The result is 2.

There is a 0 in the 4s place, so we multiply 4 times 0. The result is 0.

There is a 1 in the 8s place, so we multiply 8 times 1. The result is 8.

There is a 0 in the 16s place, so we multiply 16 times 0. The result is 0.

There is a 1 in the 32s place, so we multiply 32 times 1. The result is 32.

Now we add the results. So 32 + 0 + 8 + 0 + 2 + 0 = 42. %101010 = 42. This may seem like a rather tedious way to work with numbers, stretching what would otherwise be a relatively short and easy-to-read decimal number into a long, inefficient, and annoying string of binary, which is why we programmers have another way of writing numbers: hexadecimal!

Hexadecimal, often abbreviated to hex, is precisely what the name suggests: base 16. Hexadecimal numbers are much shorter than binary, and usually shorter than decimal too. In assembly, we put a dollar sign \$ in front of a number to make it clear that the number is hexadecimal. (Sometimes you will see 0x in front of a hexadecimal number too.) Hexadecimal has a "ones" place, a "sixteens" place, (bear with me here) a "256s" place (16 \* 16 = 256), a "65536s" place (256 \* 16 = 65536), a "16777216s" place (65536 \* 16 = 16777216), and so on. It gets really big really quickly.

But wait! In decimal, we had ten digits. Binary had two. Hexadecimal needs... sixteen digits, right? How do we even write that? Well, we use letters. In Hexadecimal, when a digit is ten, we use the letter A. When a digit is eleven, we use the letter B. C is twelve, D is thirteen, E is fourteen, and F is fifteen. (Anything past that spills over into the next digit, just like how decimal doesn't have anything over the digit 9.)

Let's use another chart to convert from hexadecimal to decimal.

| Place | 16384's | 256's | 16's | 1's |

|-------|---------|-------|------|-----|

| Digit | 9       | 9     | 2    | С   |

Just like with binary numbers, we multiply down and add across. We just have to remember that letters A-F correspond to the numbers 10-15.

There is a C in the 1s place, so we multiple 1 times 12 (C = 12). The result is 12.

There is a 2 in the 16s place, so we multiple 2 times 16. The result is 32.

There is a 9 in the 256s place, so we multiple 2 times 16. The result is 2304.

There is a 9 in the 65536s place, so we multiple 2 times 16. The result is 36864.

36864 + 2304 + 32 + 12 = 39212. That was a very large number. If we were to write it out in binary it would be %1001100100101100. Ick. Hexadecimal makes things a lot cleaner. And the best part is that every four digits in binary is equal to EXACTLY one hexadecimal digit! So if you split up that icky binary string into sections of four (%1001 %1001 %0010 %1100) every little section corresponds with one of the digits of the hexadecimal string. This makes converting between binary and hexadecimal much easier if you just memorize which 4-digit binary numbers go with which hexadecimal digits.

Okay, so everything in computers is actually binary, which can be represented more nicely in hexadecimal. But even a computer can't manage a humongous amount of binary in one large lump. It needs to organize things. So it splits up the data into sections called bytes. Every binary digit in a computer is a bit. If the bit is one, we say it is on. If it is zero, we say it is off. Every byte has 8 bits. That means each byte is an 8-digit binary number, or a 2-digit hexadecimal number. Since a single byte is two hexadecimal digits and the highest number you can write with two hexadecimal digits is \$FF (255 in decimal), a byte can store a number from 0 to 255. This is why lots of computer things have limits at 255 or 256. You know the term kilobyte, which is 1024 bytes (roughly a thousand). A megabyte is of course 1048576 bytes (roughly a million).

Finally, computers start counting with zeroes, so if I have two files, one would be labeled file 0, and the other file 1.

Here are some practice problems to do:

| Decimal | Hexadecimal | Binary |

|---------|-------------|--------|

| 10      | ?           | ?      |

| 72      | \$48        | ?      |

| ?       | ?           | 101011 |

| ?       | \$1E        | ?      |

If you can do all of these problems, you are ready to move on to the next tutorial.

If you need more help, visit the additional learning page: here

We'll be using these concepts very frequently, so make sure you have mastered them before moving on to the next tutorial.

In the next tutorial we'll be learning about how information is stored on your calculator.

## **Registers and Indirection**

## **The Registers**

If you've ever programmed in a different language, you've used something called variables to store your data temporarily. In assembly, we use registers.

There are many registers you can use in assembly. The ones we will be covering today are: A, B, C, D, E, F, H, and L, which can be paired together to form AF, BC, DE, and HL. As you probably have guessed, when a register is paired with another it can hold more information.

Recall from the last tutorial bits and bytes? H is a 1 byte register, or 8 bits, while HL is a 3 byte register pair, or 24 bits.

Now that we know about registers, it's time we learn our first instruction!

ld destination, source

What does this code do? It puts the value of source into the given destination. We can use registers as arguments for this instruction:

#### ld h,d

Puts the content of D inside H.

We can also use numbers:

ld hl,7

Puts 7 into HL.

Remember the size of the registers you are using:

ld hl,a

This not a valid instruction, as both arguments have to be 8 bit registers.

## Addresses

To fully understand what indirection is, we have to know what an address is. An address is a number that corresponds to a specific byte in RAM. Add one to the address and you go forward a byte; subtract one and you go backward a byte.

You can use addresses in place of registers with the LD instruction

```

ld hl, (133212)

```

This will put whatever is inside address 133212, the 133213th byte, and the 2 bytes after that (hl is 3 bytes), inside the hl register pair.

But why do we have parenthesis around the address? This is something called indirection.

## Indirection

Note: Indirection is slightly hard to grasp for newcomers, and we'll touch more on this later, so just do your best

Indirection tells you whether or not you are using the number as an address, or just as a number. Here the example from above:

ld hl, (133212)

How does the program know whether you are talking about the 133213th byte or the actual number 133212? The parenthesis tell the program to use the number as an address.

```

1d h1,133212 ;let's put 133212 inside h1. Note, there are no parenthesis, so we're_

→talking about the number 133212, and not the 133213th byte.

1d a,2 ;also no parenthesis, we mean 2

1d (h1),a ;we can decide later to use it as an address, by putting the parenthesis_

→around it. Now we are putting the value of A, 2, inside the address stored in h1.

```

Don't worry if you don't immediately get it, it will come to you eventually. Now it's your turn to try

ld de, (133215) ld (132918),de

If you know what's happening here, good for you! If you don't, it's ok. You'll get it later.

In the next tutorial we will learn about labels.

## Labels

Labels consist of an identifier (or symbol) followed by a colon :. The identifier can contain numbers, letters, and underscores \_, but cannot start with a number. Labels must be defined only once.

When a program is compiled, each label is replaced with a 24bit address. A label can be used to identify a string of data, a location to jump to, or a subroutine to call.

From the example program:

```

.nolist

#include "includes\ti84pce.inc"

.list

.assume ADL=1

.org userMem-2

.db tExtTok,tAsm84CeCmp

call _homeup

call _ClrScrnFull

ld hl, TutorialText

call _PutS

call _GetKey

call _ClrScrnFull

res donePrgm, (iy+doneFlags)

ret

TutorialText:

.db "Excellent job! :) You havecreated your first assembly program!",0

```

The label TutorialText is used by the compiler to store the location of the start of the string. (TutorialText now refers to the 24bit address of the start of the string.)

Here, the value of the label TutorialText is loaded into hl (the address of the start of the string) and call \_PutS displays the string located at the address in hl. \_PutS itself is also a label (defined in ti84pce.inc) that refers to the address of a subroutine built into TI-OS.

## Romcalls

Romcalls are pieces of code that run system predefined functions.

A list of romcalls can be found here, with one problem. Since this list is for the TI-83 Plus, some of the romcalls are missing or outdated. Also, the romcalls on the +CE are prefixed with a single underscore.

How does the assembler know where the romcalls on the TI-84+CE are? Surely they must be in a different location then the CE? The answer lies in the .inc file that you include at the start of every program.

#include "includes\ti84pce.inc"

Inside is a list of addresses that define where the romcalls (and other important items) are located. Each calculator has a different .inc file.

So how do we call a romcall?

call \_PutS

This will call the romcall \_PutS, which as you can see in the system routines pdf, reads the string inside the address in HL.

Recall from the very first tutorial the example program

```

.nolist

#include "includes\ti84pce.inc"

.list

.assume ADL=1

.org userMem-2

.db tExtTok,tAsm84CeCmp

call _homeup

call _ClrScrnFull

ld hl,TutorialText

call _PutS

call _GetKey

call _ClrScrnFull

res donePrgm, (iy+doneFlags)

ret

```

```

TutorialText:

.db "Excellent job! :) You havecreated your first assembly program!",0

```

Now that we know romcalls, we can figure out what each line does.

```

call _homeup

call _ClrScrnFull

```

\_HomeUp isn't in the System Routines file, but it and \_ClrScrnFull set up for the text output by resetting the screen.

```

ld hl,TutorialText

call _PutS

```

From the last tutorial, we learned about labels, and how they are converted to addresses at runtime. Since \_PutS reads from HL as an address, we can just put the address number, and not the contents inside HL. This means we do not use indirection and we do not need parenthesis.

\_PutS reads a null terminating string from HL. All that means is that the string ends in 0.

```

call _GetKey

call _ClrScrnFull

res donePrgm,(iy+doneFlags)

ret

```

We call \_GetKey to pause the program until a key is pressed. Afterword, we clear the screen again using \_ClrScrnFull. Don't worry about the second to last line for now, we'll learn what it does later. Finally, the program ends.

Once again, you can learn more about each romcall in the PDF above. From now on, if there is a romcall you don't recognize, use the PDF.

The next tutorial's contents are unknown. How mysterious!

Hooks

## Arithmetic Instructions

## ADC

### ADC M,N Add with Carry

#### Description

Adds  $\mathbb M,$   $\mathbb N,$  and the carry flag (+0 or +1) and stores the result in  $\mathbb M.$

M += N + Carry

#### Uses

- Storing the state of the carry flag in either A or HL with adc a, 0 or ld bc/de, 0 \ adc hl, bc/de

- 16 bit addition which checks if the result is zero (see Notes)

- Can be useful otherwise in very specific situations

|         | Regis-   | 8-bit                                     | 16-bit (non-ADL)                                               | 24-bit (ADL)                   |  |  |  |

|---------|----------|-------------------------------------------|----------------------------------------------------------------|--------------------------------|--|--|--|

|         | ter/Flag |                                           |                                                                |                                |  |  |  |

|         | М        | Set to the result of M + N + Carry        |                                                                |                                |  |  |  |

|         | S flag   | Set if the result is negative; else reset |                                                                |                                |  |  |  |

|         | Z flag   | Set if the result is 0; else reset        |                                                                |                                |  |  |  |

| Results | H flag   | Set if carry from bit 3; else             | if carry from bit 3; else Set if carry from bit 11; else reset |                                |  |  |  |

|         |          | reset                                     |                                                                |                                |  |  |  |

|         | P/V flag | Set if overflow; else reset               |                                                                |                                |  |  |  |

|         | N flag   | Reset                                     |                                                                |                                |  |  |  |

|         | C flag   | Set if carry from bit 7; else             | Set if carry from bit 15; else                                 | Set if carry from bit 23; else |  |  |  |

|         |          | reset                                     | reset                                                          | reset                          |  |  |  |

|                      | Instruction  | Opcode        | CC (ADL/non-ADL) | CC (.S) | CC (.L) |

|----------------------|--------------|---------------|------------------|---------|---------|

|                      | adc a,a      | \$8F          | 1F               | Х       | Х       |

|                      | adc a,b      | \$88          | 1F               | Х       | X       |

|                      | adc a,c      | \$89          | 1F               | Х       | X       |

|                      | adc a,d      | \$8A          | 1F               | Х       | X       |

|                      | adc a,e      | \$8B          | 1F               | Х       | X       |

|                      | adc a,h      | \$8C          | 1F               | Х       | X       |

|                      | adc a,1      | \$8D          | 1F               | Х       | X       |

|                      | adc a,ixh    | \$DD, \$8C    | 2F               | Х       | X       |

| Allowed Instructions | adc a,ixl    | \$DD, \$8D    | 2F               | Х       | X       |

| Anowed Instructions  | adc a,iyh    | \$FD, \$8C    | 2F               | Х       | Х       |

|                      | adc a,iyl    | \$FD, \$8D    | 2F               | Х       | Х       |

|                      | adc a,(hl)   | \$8E          | 1F + 1R          | 2F + 1R | 2F + 1R |

|                      | adc a,(ix+n) | \$DD, \$8E, n | 3F + 1R          | 4F + 1R | 4F + 1R |

|                      | adc a,(iy+n) | \$FD, \$8E, n | 3F + 1R          | 4F + 1R | 4F + 1R |

|                      | adc a,n      | \$CE, n       | 2F               | Х       | X       |

|                      | adc hl,bc    | \$ED, \$4A    | 2F               | 3F      | 3F      |

|                      | adc hl,de    | \$ED, \$5A    | 2F               | 3F      | 3F      |

|                      | adc hl,hl    | \$ED, \$6A    | 2F               | 3F      | 3F      |

|                      | adc hl,sp    | \$ED, \$7A    | 2F               | 3F      | 3F      |

- Unlike ADD, this instruction **does not** support using the index registers IX and IY as the first operand.

- Unlike ADD, this instruction **does** modify the Z flag when doing 16-bit and 24-bit addition.

See Also ADD, SBC, SUB

## ADD

### ADD M,N Add

### Description

Adds  ${\tt M}$  and  ${\tt N}$  and stores the result in  ${\tt M}.$

M += N

|         | Regis-<br>ter/Flag | 8-bit                              | 16-bit (non-ADL)                               | 24-bit (ADL)              |  |

|---------|--------------------|------------------------------------|------------------------------------------------|---------------------------|--|

|         | М                  | Set to the result of $M + N$       |                                                |                           |  |

| Results | S flag             | Set if the result is negative;     | Not affected                                   |                           |  |

|         |                    | else reset                         |                                                |                           |  |

|         | Z flag             | Set if the result is 0; else reset | et if the result is 0; else reset Not affected |                           |  |

|         | H flag             | Set if carry from bit 3; else      | Set if carry from bit 11; else reset           |                           |  |

|         |                    | reset                              |                                                |                           |  |

|         | P/V flag           | Set if overflow; else reset        | Not affected                                   |                           |  |

|         | N flag             | Reset                              |                                                |                           |  |

|         | C flag             | Set if carry from bit 7; else      | Set if carry from bit 15;                      | Set if carry from bit 23; |  |

|         |                    | reset                              | else reset                                     | else reset                |  |

|                      | Instruction  | Opcode        | CC (ADL/non-ADL) | CC (.S) | CC (.L) |

|----------------------|--------------|---------------|------------------|---------|---------|

|                      | add a,a      | \$87          | 1F               | Х       | Х       |

|                      | add a,b      | \$80          | 1F               | Х       | Х       |

|                      | add a,c      | \$81          | 1F               | Х       | Х       |

|                      | add a,d      | \$82          | 1F               | Х       | Х       |

|                      | add a,e      | \$83          | 1F               | Х       | Х       |

|                      | add a,h      | \$84          | 1F               | Х       | Х       |

|                      | add a,l      | \$85          | 1F               | Х       | Х       |

|                      | add a,ixh    | \$DD, \$84    | 2F               | Х       | Х       |

|                      | add a,ixl    | \$DD, \$85    | 2F               | Х       | Х       |

|                      | add a,iyh    | \$FD, \$84    | 2F               | Х       | Х       |

|                      | add a,iyl    | \$FD, \$85    | 2F               | Х       | Х       |

|                      | add a,(hl)   | \$86          | 1F + 1R          | 2F + 1R | 2F + 1R |

| Allowed Instructions | add a,(ix+n) | \$DD, \$86, n | 3F + 1R          | 4F + 1R | 4F + 1R |

| Anoweu msu ucuons    | add a,(iy+n) | \$FD, \$86, n | 3F + 1R          | 4F + 1R | 4F + 1R |

|                      | add a,n      | \$C6, n       | 2F               | Х       | Х       |

|                      | add hl,bc    | \$0A          | 1F               | 2F      | 2F      |

|                      | add hl,de    | \$1A          | 1F               | 2F      | 2F      |

|                      | add hl,hl    | \$2A          | 1F               | 2F      | 2F      |

|                      | add hl,sp    | \$3A          | 1F               | 2F      | 2F      |

|                      | add ix,bc    | \$DD, \$0A    | 2F               | 3F      | 2F      |

|                      | add ix,de    | \$DD, \$1A    | 2F               | 3F      | 3F      |

|                      | add ix,ix    | \$DD, \$2A    | 2F               | 3F      | 3F      |

|                      | add ix,sp    | \$DD, \$3A    | 2F               | 3F      | 3F      |

|                      | add iy,bc    | \$FD, \$0A    | 2F               | 3F      | 3F      |

|                      | add iy,de    | \$FD, \$1A    | 2F               | 3F      | 3F      |

|                      | add iy,iy    | \$FD, \$2A    | 2F               | 3F      | 3F      |

|                      | add iy,sp    | \$FD, \$3A    | 2F               | 3F      | 3F      |

- Unlike ADC, this instruction **does** support using the index registers IX and IY as the first operand. This is the only difference in the allowed instructions between the two.

- This instruction **does not** modify the S, Z, and P/V flags when doing 16-bit and 24-bit addition. For that, you can use ADC.

- Like most instructions, HL, IX, and IY are mutually exclusive. I.e. they cannot be used in the same instructions.

See Also ADC, SBC, SUB

## СР

### CP M,N Compare

#### Description

Subtracts  ${\tt N}$  from  ${\tt M}$  (and updates the flags accordingly), but doesn't modify either operand.

M – N

Uses

· Comparing two bytes

|         | Register/Flag | 8-bit                                     |

|---------|---------------|-------------------------------------------|

|         | S flag        | Set if the result is negative; else reset |

|         | Z flag        | Set if $M = N$                            |

| Results | H flag        | Set if borrow from bit 4; else reset      |

|         | ₽/V flag      | Set if overflow; else reset               |

|         | N flag        | Set                                       |

|         | C flag        | Set if borrow; else reset                 |

|                      | Instruction | Opcode        | CC (ADL/non-ADL) | CC (.S) | CC (.L) |

|----------------------|-------------|---------------|------------------|---------|---------|

|                      | cp a,a      | \$BF          | 1F               | Х       | Х       |

|                      | cp a,b      | \$B8          | 1F               | Х       | Х       |

|                      | cp a,c      | \$B9          | 1F               | Х       | Х       |

|                      | cp a,d      | \$BA          | 1F               | Х       | Х       |

|                      | cp a,e      | \$BB          | 1F               | Х       | Х       |

|                      | cp a,h      | \$BC          | 1F               | Х       | Х       |

| Allowed Instructions | cp a,l      | \$BD          | 1F               | Х       | Х       |

| Anoweu msu ucuons    | cp a,ixh    | \$DD, \$BC    | 2F               | Х       | Х       |

|                      | cp a,ixl    | \$DD, \$BD    | 2F               | Х       | Х       |

|                      | cp a,iyh    | \$FD, \$BC    | 2F               | Х       | Х       |

|                      | cp a,iyl    | \$FD, \$BD    | 2F               | Х       | Х       |

|                      | cp a,(hl)   | \$BE          | 1F + 1R          | 2F + 1R | 2F + 1R |

|                      | cp a,(ix+n) | \$DD, \$BE, n | 3F + 1R          | 4F + 1R | 4F + 1R |

|                      | cp a,(iy+n) | \$FD, \$BE, n | 3F + 1R          | 4F + 1R | 4F + 1R |

|                      | cp a,n      | \$FE, n       | 2F               | Х       | Х       |

### • When using CP with signed integers, the flags are set as follows:

- Z means M = N

- NZ means M N

- C means M < N

- NC means M  $\,\rm N$

### See Also SUB, SBC, CPI, CPIR, CPD, CPDR

## DAA

DAA Decimal Adjust Accumulator

#### Description

Does cool stuff with binary-coded decimal.

### Uses

• Probably useful for BCD arithmetic?

|         | Register/Flag | 8-bit                                         |

|---------|---------------|-----------------------------------------------|

| Results | S flag        | Set to the 7th bit of the result              |

|         | Z flag        | Set if the result is 0; else reset            |

|         | H flag        | Really complicated                            |

|         | ₽/V flag      | Set if the result has even parity; else reset |

|         | N flag        | Not affected                                  |

|         | C flag        | Really complicated                            |

| Allowed Instructions | Instruction | Opcode | CC (ADL/non-ADL) | CC (.S) | CC (.L) |

|----------------------|-------------|--------|------------------|---------|---------|

|                      | daa         | \$27   | 1F               | Х       | Х       |

#### • When using CP with signed integers, the flags are set as follows:

- Z means M = N

- NZ means M N

- C means M < N

- NC means M  $\,$  N

See Also ADD, ADC, RLD, RRD, SBC, SUB

## DEC

#### DEC M Decrement

#### Description

Decrements M by 1.

#### Results

| Allowed Instructions | Instruction | Opcode | CC (ADL/non-ADL) | CC (.S) | CC (.L) |

|----------------------|-------------|--------|------------------|---------|---------|

| Anowed Instructions  |             |        |                  |         |         |

#### Notes

• While this instruction can be combined with a jr nz, LoopLabel to create a great 8-bit loop, using dec with a 16-bit or 24-bit operand will not alter the flags, so you'll need another method of checking if the register pair is zero.

See Also INC

## INC

INC M Increment

#### Description

Increments M by 1. M += 1

|                | Register/Flag 8-bit |             | 16-bit (non-ADL)  | 24-bit (ADL)         |                  |         |

|----------------|---------------------|-------------|-------------------|----------------------|------------------|---------|

|                | М                   | Set to the  | result of $M +$   | 1                    |                  |         |

|                | S flag              | Set if the  | result is negativ | ve; else reset       | Not affected     |         |

| Results Z flag |                     | Set if the  | result is 0; else | reset                | Not affected     |         |

| Results        | H flag              | Set if car  | ry from bit 3; el | se reset             | Not affected     |         |

|                | P/V flag            | Set if M w  | as \$7F before o  | peration; else reset | Not affected     |         |

|                | N flag              | Reset       |                   |                      | Not affected     |         |

|                | C flag              | Not affec   | ted               |                      |                  |         |

|                |                     | Instruction | Opcode            | CC (ADL/non-ADL      | _)   CC (.S)     | CC (.L) |

|                |                     | inc a       | \$3C              | 1F                   | X X              | X       |

|                |                     | inc b       | \$04              | 1F                   | X                | X       |

|                |                     | inc c       | \$0C              | 1F                   | X                | X       |

|                |                     | inc d       | \$14              | 1F                   | X                | X       |

|                |                     | inc e       | \$1C              | 1F                   | X                | X       |

|                |                     | inc h       | \$24              | 1F                   | X                | X       |

|                |                     | inc l       | \$2C              | 1F                   | X                | X       |

|                |                     | inc ixh     | \$DD, \$24        | 2F                   | X                | X       |

|                |                     | inc ixl     | \$DD, \$2C        | 2F                   | X                | X       |

| Allowed        | Instructions        | inc iyh     | \$FD, \$24        | 2F                   | X                | X       |

|                |                     | inc iyl     | \$FD, \$2C        | 2F                   | X                | Х       |

|                |                     | inc (hl)    | \$34              | 1F + 1R + 1W + 1     | 2F + 1R + 1W + 1 |         |

|                |                     | inc (ix+n)  | \$DD, \$34, n     | 3F + 1R + 1W + 1     | 4F + 1R + 1W + 1 |         |

|                |                     | inc (iy+n)  | \$FD, \$34, n     | 3F + 1R + 1W + 1     | 4F + 1R + 1W + 1 |         |

|                |                     | inc bc      | \$ED, \$0B        | 1F                   | 2F               | 2F      |

|                |                     | inc de      | \$ED, \$1B        | 1F                   | 2F               | 2F      |

|                |                     | inc hl      | \$ED, \$23        | 1F                   | 2F               | 2F      |

|                |                     | inc sp      | \$ED, \$3B        | 1F                   | 2F               | 2F      |

|                |                     | inc ix      | \$DD, \$23        | 2F                   | 3F               | 3F      |

|                |                     | inc iy      | \$ED, \$23        | 2F                   | 3F               | 3F      |

• Keep in mind that the flags are not altered when using this instruction with a 16-bit and 24-bit operand.

See Also DEC

# **Bit Manipulation**

## BIT

### BIT b,M Test Bit

### Description

Checks the b``th bit of ``M and stores the inverse in the Z flag. b must be a hard-coded number between 0 and 7.

|                     | Register/Flag | 8-bit              | 16-bit (non-ADL) | 24-bit (ADL) |

|---------------------|---------------|--------------------|------------------|--------------|

|                     | S flag        | Undefined          |                  |              |

|                     | Z flag        | oit b of M is zero |                  |              |

| Results H flag Set  |               |                    |                  |              |

|                     | ₽/V flag      | Undefined          |                  |              |

|                     | N flag        | Reset              |                  |              |

| C flag Not affected |               |                    |                  |              |

### **Allowed Instructions**

| Instruction            | Opcode              | CC (ADL/non-ADL) | CC (.S) | CC (.L) |  |

|------------------------|---------------------|------------------|---------|---------|--|

| bit 0,a                | \$CB, \$47          | 2F               | Х       | Х       |  |

| bit 0,b                | \$CB, \$40          | 2F               | Х       | Х       |  |

| bit 0,c                | \$CB, \$41          | 2F               | Х       | Х       |  |

| bit 0,d                | \$CB, \$42          | 2F               | Х       | Х       |  |

| bit 0,e                | \$CB, \$43          | 2F               | X       | Х       |  |

| bit 0,h                | \$CB, \$44          | 2F               | X       | Х       |  |

| bit 0,1                | \$CB, \$45          | 2F               | X       | Х       |  |

| bit 0,(hl)             | \$CB, \$46          | 2F + 1R          | 3F + 1R | 3F + 1R |  |

| bit 0,(ix+n)           | \$DD, \$CB, n, \$46 | 4F + 1R          | 5F + 1R | 5F + 1R |  |

| bit 0,(iy+n)           | \$FD, \$CB, n, \$46 | 4F + 1R          | 5F + 1R | 5F + 1R |  |

| bit 1,a                | \$CB, \$4F          | 2F               | Х       | Х       |  |

| bit 1,b                | \$CB, \$48          | 2F               | Х       | Х       |  |

| Continued on next page |                     |                  |         |         |  |

|                               |                                   | tinued from previous p | -            |           |

|-------------------------------|-----------------------------------|------------------------|--------------|-----------|

| Instruction                   | Opcode                            | CC (ADL/non-ADL)       | CC (.S)      | CC (.L)   |

| bit 1,c                       | \$CB, \$49                        | 2F                     | X            | Х         |

| bit 1,d                       | \$CB, \$4A                        | 2F                     | Х            | Х         |

| bit 1,e                       | \$CB, \$4B                        | 2F                     | Х            | Х         |

| bit 1,h                       | \$CB, \$4C                        | 2F                     | Х            | Х         |

| bit 1,l                       | \$CB, \$4D                        | 2F                     | X            | Х         |

| bit 1,(hl)                    | \$CB, \$4E                        | 2F + 1R                | 3F + 1R      | 3F + 1R   |

| bit 1,(ix+n)                  | \$DD, \$CB, n, \$4E               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 1,(iy+n)                  | \$FD, \$CB, n, \$4E               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 2,a                       | \$CB, \$57                        | 2F                     | X            | Х         |

| bit 2,b                       | \$CB, \$50                        | 2F                     | X            | Х         |

| bit 2,c                       | \$CB, \$51                        | 2F                     | X            | Х         |

| bit 2,d                       | \$CB, \$52                        | 2F                     | Х            | Х         |

| bit 2,e                       | \$CB, \$53                        | 2F                     | Х            | Х         |

| bit 2,h                       | \$CB, \$54                        | 2F                     | Х            | Х         |

| bit 2,1                       | \$CB, \$55                        | 2F                     | X            | Х         |

| bit 2,(hl)                    | \$CB, \$56                        | 2F + 1R                | 3F + 1R      | 3F + 1R   |

| bit $2,(ix+n)$                | \$DD, \$CB, n, \$56               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 2,(iy+n)                  | \$FD, \$CB, n, \$56               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 3,a                       | \$CB, \$5F                        | 2F                     | X            | Х         |

| bit 3,b                       | \$CB, \$58                        | 2F                     | X            | Х         |

| bit 3,c                       | \$CB, \$59                        | 2F                     | X            | Х         |

| bit 3,d                       | \$CB, \$5A                        | 2F                     | X            | X         |

| bit 3,e                       | \$CB, \$5B                        | 2F                     | X            | X         |

| bit 3,h                       | \$CB, \$5C                        | 2F                     | X            | X         |

| bit 3,1                       | \$CB, \$5D                        | 2F                     | X            | X         |

| bit 3,(hl)                    | \$CB, \$5E                        | 2F + 1R                | 3F + 1R      | 3F + 1R   |

| bit 3,(ix+n)                  | \$DD, \$CB, n, \$5E               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit $3,(iy+n)$                | \$FD, \$CB, n, \$5E               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 4,a                       | \$CB, \$67                        | 2F                     | X            | X         |

| bit 4,b                       | \$CB, \$60                        | 2F                     | X            | X         |

| bit 4,c                       | \$CB, \$61                        | 2F                     | X            | X         |

| bit 4,d                       | \$CB, \$62                        | 2F                     | X            | X         |

| bit 4,e                       | \$CB, \$63                        | 2F                     | X            | X         |

| bit 4,e                       | \$CB, \$63<br>\$CB, \$64          | 2F                     | X            | X         |

|                               | \$CB, \$65                        | 2F                     | X            | X         |

| bit 4,1<br>bit 4 (b1)         |                                   |                        |              |           |

| bit 4,(hl)<br>bit 4 (in $p$ ) | \$CB, \$66<br>\$DD, \$CB, n, \$66 | 2F + 1R                | 3F + 1R      | 3F + 1R   |

| bit $4$ ,(ix+n)               |                                   | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 4,(iy+n)                  | \$FD, \$CB, n, \$66               | 4F + 1R                | 5F + 1R<br>X | 5F + 1R   |

| bit 5,a                       | \$CB, \$6F                        | 2F                     |              | X         |

| bit 5,b                       | \$CB, \$68                        | 2F                     | X            | X         |

| bit 5,c                       | \$CB, \$69                        | 2F                     | X            | X         |

| bit 5,d                       | \$CB, \$6A                        | 2F                     | X            | X         |

| bit 5,e                       | \$CB, \$6B                        | 2F                     | X            | X         |

| bit 5,h                       | \$CB, \$6C                        | 2F                     | X            | X         |

| bit 5,1                       | \$CB, \$6D                        | 2F                     | X            | X         |

| bit 5,(hl)                    | \$CB, \$6E                        | 2F + 1R                | 3F + 1R      | 3F + 1R   |

| bit 5,(ix+n)                  | \$DD, \$CB, n, \$6E               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 5,(iy+n)                  | \$FD, \$CB, n, \$6E               | 4F + 1R                | 5F + 1R      | 5F + 1R   |

| bit 6,a                       | \$CB, \$77                        | 2F                     | X            | Х         |

|                               |                                   | Cont                   | tinued on r  | lext page |

Table 9.1 – continued from previous page

|              | Table 9.1 – Continued from previous page |                  |         |         |  |  |

|--------------|------------------------------------------|------------------|---------|---------|--|--|

| Instruction  | Opcode                                   | CC (ADL/non-ADL) | CC (.S) | CC (.L) |  |  |

| bit 6,b      | \$CB, \$70                               | 2F               | X       | Х       |  |  |

| bit 6,c      | \$CB, \$71                               | 2F               | Х       | Х       |  |  |

| bit 6,d      | \$CB, \$72                               | 2F               | Х       | Х       |  |  |

| bit 6,e      | \$CB, \$73                               | 2F               | Х       | Х       |  |  |

| bit 6,h      | \$CB, \$74                               | 2F               | Х       | Х       |  |  |

| bit 6,1      | \$CB, \$75                               | 2F               | Х       | Х       |  |  |

| bit 6,(hl)   | \$CB, \$76                               | 2F + 1R          | 3F + 1R | 3F + 1R |  |  |

| bit 6,(ix+n) | \$DD, \$CB, n, \$76                      | 4F + 1R          | 5F + 1R | 5F + 1R |  |  |

| bit 6,(iy+n) | \$FD, \$CB, n, \$76                      | 4F + 1R          | 5F + 1R | 5F + 1R |  |  |

| bit 7,a      | \$CB, \$7F                               | 2F               | Х       | Х       |  |  |

| bit 7,b      | \$CB, \$78                               | 2F               | Х       | Х       |  |  |

| bit 7,c      | \$CB, \$79                               | 2F               | Х       | Х       |  |  |

| bit 7,d      | \$CB, \$7A                               | 2F               | Х       | Х       |  |  |

| bit 7,e      | \$CB, \$7B                               | 2F               | Х       | Х       |  |  |

| bit 7,h      | \$CB, \$7C                               | 2F               | Х       | Х       |  |  |

| bit 7,1      | \$CB, \$7D                               | 2F               | Х       | Х       |  |  |

| bit 7,(hl)   | \$CB, \$7E                               | 2F + 1R          | 3F + 1R | 3F + 1R |  |  |

| bit 7,(ix+n) | \$DD, \$CB, n, \$7E                      | 4F + 1R          | 5F + 1R | 5F + 1R |  |  |

| bit 7,(iy+n) | \$FD, \$CB, n, \$7E                      | 4F + 1R          | 5F + 1R | 5F + 1R |  |  |

| Table 9.1 | - continued | from | previous page |  |

|-----------|-------------|------|---------------|--|

| 10010 0.1 | 0011111000  |      | proviouo pugo |  |

- Interestingly enough, the index registers IXH, IXL, IYH, and IYL cannot be used in this instruction, yet (IX+n) and (IY+n) are allowed as operands.

- The z flag is set as follows:

- Z means the bit is zero

- NZ means the bit is one (non-zero)

See Also RES, SET

## RES

### RES b,M Reset Bit

### Description

Sets the b``th bit of ``M to zero. b must be a hard-coded number between 0 and 7.

|         | Register/Flag | 8-bit   16-bit (non-ADL)   24-bit (ADL) |  |  |  |

|---------|---------------|-----------------------------------------|--|--|--|

|         | М             | The "b"th bit of M is set to zero       |  |  |  |

|         | S flag        | Not affected                            |  |  |  |

| Results | Not affected  |                                         |  |  |  |

| Results | H flag        | Not affected                            |  |  |  |

|         | ₽/V flag      | Not affected                            |  |  |  |

|         | N flag        | Not affected                            |  |  |  |

|         | C flag        | Not affected                            |  |  |  |

#### **Allowed Instructions**

| Instruction                                                                 | Opcode                   | CC (ADL/non-ADL)                     | CC (.S)                              | CC (.L)                              |

|-----------------------------------------------------------------------------|--------------------------|--------------------------------------|--------------------------------------|--------------------------------------|

| res 0,a                                                                     | \$CB, \$87               | 2F                                   | X                                    | X                                    |

| res 0,b                                                                     | \$CB, \$80               | 2F                                   | Х                                    | Х                                    |

| res 0,c                                                                     | \$CB, \$81               | 2F                                   | X                                    | X                                    |

| res 0,d                                                                     | \$CB, \$82               | 2F                                   | Х                                    | X                                    |

| res 0,e                                                                     | \$CB, \$83               | 2F                                   | Х                                    | X                                    |

| res 0,h                                                                     | \$CB, \$84               | 2F                                   | Х                                    | X                                    |

| res 0,1                                                                     | \$CB, \$85               | 2F                                   | X                                    | X                                    |

| res 0,(hl)                                                                  | \$CB, \$86               | 2F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     |

| res 0,(ix+n)                                                                | \$DD, \$CB, \$86, n      | 4F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     |

| res 0,(iy+n)                                                                | \$FD, \$CB, \$86, n      | 4F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     |

| res 1,a                                                                     | \$CB, \$8F               | 2F                                   | X                                    | X                                    |

| res 1,b                                                                     | \$CB, \$88               | 2F                                   | X                                    | X                                    |

| res 1,c                                                                     | \$CB, \$89               | 2F                                   | X                                    | X                                    |

| res 1,d                                                                     | \$CB, \$8A               | 2F                                   | X                                    | X                                    |

| res 1,e                                                                     | \$CB, \$8B               | 2F                                   | X                                    | X                                    |

| res 1,h                                                                     | \$CB, \$8C               | 2F                                   | X                                    | X                                    |

| res 1,1                                                                     | \$CB, \$8C               | 2F                                   | X                                    | X                                    |

| res 1,(hl)                                                                  | \$CB, \$8D<br>\$CB, \$8E | 2F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     |

| $\frac{100}{100} res 1,(in)$                                                | \$DD, \$CB, \$8E, n      | 4F + 1R + 1W + 1<br>4F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 |

| $\frac{1 \text{ res } 1,(1x+11)}{1 \text{ res } 1,(1y+11)}$                 | \$FD, \$CB, \$8E, n      | 4F + 1R + 1W + 1<br>4F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 |

| $\frac{1000}{1000} res 2,a$                                                 | \$CB, \$97               | 2F                                   | X                                    | $\frac{31 + 111 + 1111 + 11111}{X}$  |

| res 2,b                                                                     | \$CB, \$97<br>\$CB, \$90 | 2F                                   | X                                    | X                                    |

| res 2,0                                                                     | \$CB, \$90<br>\$CB, \$91 | 2F                                   | X                                    | X                                    |

|                                                                             | \$CB, \$91<br>\$CB, \$92 | 2F<br>2F                             | X                                    | X                                    |

| res 2,d                                                                     | -                        | 2F<br>2F                             | X<br>X                               | X                                    |

| res 2,e                                                                     | \$CB, \$93<br>\$CB, \$94 | 2F<br>2F                             | X                                    | X                                    |

| res 2,h                                                                     | \$СВ, \$94<br>\$CB, \$95 | 2F<br>2F                             | X                                    | X                                    |

| res 2,1<br>res 2,(hl)                                                       | эсв, \$95<br>\$CB, \$96  | 2F<br>2F + 1R + 1W + 1               | $\frac{A}{3F + 1R + 1W + 1}$         | $\frac{A}{3F + 1R + 1W + 1}$         |

| $\frac{108 2,(11)}{108 2,(1x+n)}$                                           | \$DD, \$CB, \$96, n      | 4F + 1R + 1W + 1<br>4F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 |

| $\frac{1 \text{ res } 2,(1 \text{ x}+1)}{1 \text{ res } 2,(1 \text{ y}+1)}$ | \$FD, \$CB, \$96, n      | 4F + 1R + 1W + 1<br>4F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 | 5F + 1R + 1W + 1<br>5F + 1R + 1W + 1 |

| $\frac{108 2,(1y+11)}{108 3,a}$                                             | \$CB, \$9F               | 2F                                   | X                                    | X                                    |

|                                                                             |                          | 2F<br>2F                             | X                                    | X                                    |

| res 3,b<br>res 3,c                                                          | \$CB, \$98               | 2F<br>2F                             | X                                    | X                                    |

|                                                                             | \$CB, \$99               | 2F<br>2F                             | X                                    | X                                    |

| res 3,d                                                                     | \$CB, \$9A               |                                      |                                      |                                      |

| res 3,e                                                                     | \$CB, \$9B               | 2F                                   | X                                    | X                                    |

| res 3,h                                                                     | \$CB, \$9C               | 2F                                   | X                                    | X                                    |

| res 3,1                                                                     | \$CB, \$9D               | 2F                                   | X                                    | X                                    |

| res 3,(hl)                                                                  | \$CB, \$9E               | 2F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     |

| res $3,(ix+n)$                                                              | \$DD, \$CB, \$9E, n      | 4F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     |

| res 3,(iy+n)                                                                | \$FD, \$CB, \$9E, n      | 4F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     |

| res 4,a                                                                     | \$CB, \$A7               | 2F                                   | X                                    | X                                    |

| res 4,b                                                                     | \$CB, \$A0               | 2F                                   | X                                    | X                                    |

| res 4,c                                                                     | \$CB, \$A1               | 2F                                   | X                                    | X                                    |

| res 4,d                                                                     | \$CB, \$A2               | 2F                                   | X                                    | X                                    |

| res 4,e                                                                     | \$CB, \$A3               | 2F                                   | X                                    | X                                    |

| res 4,h                                                                     | \$CB, \$A4               | 2F                                   | X                                    | X                                    |

| res 4,1                                                                     | \$CB, \$A5               | 2F                                   | X                                    | X                                    |

| res 4,(hl)                                                                  | \$CB, \$A6               | 2F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     | 3F + 1R + 1W + 1                     |

| res 4,(ix+n)                                                                | \$DD, \$CB, \$A6, n      | 4F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     |

| res 4,(iy+n)                                                                | \$FD, \$CB, \$A6, n      | 4F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     | 5F + 1R + 1W + 1                     |

|                                                                             |                          |                                      | Conti                                | nued on next page                    |

| Instruction  | Opcode              | CC (ADL/non-ADL) | CC (.S)          | CC (.L)          |

|--------------|---------------------|------------------|------------------|------------------|

| res 5,a      | \$CB, \$AF          | 2F               | Х                | Х                |

| res 5,b      | \$CB, \$A8          | 2F               | Х                | Х                |

| res 5,c      | \$CB, \$A9          | 2F               | Х                | Х                |

| res 5,d      | \$CB, \$AA          | 2F               | Х                | Х                |

| res 5,e      | \$CB, \$AB          | 2F               | Х                | Х                |

| res 5,h      | \$CB, \$AC          | 2F               | Х                | Х                |

| res 5,1      | \$CB, \$AD          | 2F               | Х                | Х                |

| res 5,(hl)   | \$CB, \$AE          | 2F + 1R + 1W + 1 | 3F + 1R + 1W + 1 | 3F + 1R + 1W + 1 |

| res 5,(ix+n) | \$DD, \$CB, \$AE, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| res 5,(iy+n) | \$FD, \$CB, \$AE, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| res 6,a      | \$CB, \$B7          | 2F               | Х                | Х                |

| res 6,b      | \$CB, \$B0          | 2F               | Х                | Х                |

| res 6,c      | \$CB, \$B1          | 2F               | Х                | Х                |

| res 6,d      | \$CB, \$B2          | 2F               | Х                | Х                |

| res 6,e      | \$CB, \$B3          | 2F               | Х                | Х                |

| res 6,h      | \$CB, \$B4          | 2F               | Х                | Х                |

| res 6,1      | \$CB, \$B5          | 2F               | Х                | Х                |

| res 6,(hl)   | \$CB, \$B6          | 2F + 1R + 1W + 1 | 3F + 1R + 1W + 1 | 3F + 1R + 1W + 1 |

| res 6,(ix+n) | \$DD, \$CB, \$B6, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| res 6,(iy+n) | \$FD, \$CB, \$B6, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| res 7,a      | \$CB, \$BF          | 2F               | Х                | Х                |

| res 7,b      | \$CB, \$B8          | 2F               | Х                | Х                |

| res 7,c      | \$CB, \$B9          | 2F               | Х                | Х                |

| res 7,d      | \$CB, \$BA          | 2F               | Х                | Х                |

| res 7,e      | \$CB, \$BB          | 2F               | Х                | Х                |

| res 7,h      | \$CB, \$BC          | 2F               | Х                | Х                |

| res 7,1      | \$CB, \$BD          | 2F               | Х                | Х                |

| res 7,(hl)   | \$CB, \$BE          | 2F + 1R + 1W + 1 | 3F + 1R + 1W + 1 | 3F + 1R + 1W + 1 |

| res 7,(ix+n) | \$DD, \$CB, \$BE, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| res 7,(iy+n) | \$FD, \$CB, \$BE, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

Table 9.2 – continued from previous page

• Interestingly enough, the index registers IXH, IXL, IYH, and IYL cannot be used in this instruction, yet (IX+n) and (IY+n) are allowed as operands.

See Also BIT, SET

## SET

### SET b,M Set Bit

### Description

Sets the b``th bit of ``M to one. b must be a hard-coded number between 0 and 7.

|         | Register/Flag | 8-bit                            | 16-bit (non-ADL) | 24-bit (ADL) |  |

|---------|---------------|----------------------------------|------------------|--------------|--|

|         | М             | The "b"th bit of M is set to one |                  |              |  |

|         | S flag        | Not af                           | Not affected     |              |  |

| Results | t affected    |                                  |                  |              |  |

| Results | H flag        | Not af                           | fected           |              |  |

|         | P/V flag      | Not affected                     |                  |              |  |

|         | N flag        | Not affected                     |                  |              |  |

|         | C flag        | Not affected                     |                  |              |  |

## **Allowed Instructions**

| Instruction            | Opcode              | CC (ADL/non-ADL) | CC (.S)          | CC (.L)          |

|------------------------|---------------------|------------------|------------------|------------------|

| set 0,a                | \$CB, \$C7          | 2F               | X                | X                |

| set 0,b                | \$CB, \$C0          | 2F               | Х                | Х                |

| set 0,c                | \$CB, \$C1          | 2F               | Х                | Х                |

| set 0,d                | \$CB, \$C2          | 2F               | Х                | Х                |

| set 0,e                | \$CB, \$C3          | 2F               | Х                | Х                |

| set 0,h                | \$CB, \$C4          | 2F               | Х                | Х                |

| set 0,1                | \$CB, \$C5          | 2F               | Х                | Х                |

| set 0,(hl)             | \$CB, \$C6          | 2F + 1R + 1W + 1 | 3F + 1R + 1W + 1 | 3F + 1R + 1W + 1 |

| set 0,(ix+n)           | \$DD, \$CB, \$C6, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| set 0,(iy+n)           | \$FD, \$CB, \$C6, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| set 1,a                | \$CB, \$CF          | 2F               | Х                | Х                |

| set 1,b                | \$CB, \$C8          | 2F               | Х                | Х                |

| set 1,c                | \$CB, \$C9          | 2F               | Х                | Х                |

| set 1,d                | \$CB, \$CA          | 2F               | Х                | Х                |

| set 1,e                | \$CB, \$CB          | 2F               | Х                | Х                |

| set 1,h                | \$CB, \$CC          | 2F               | Х                | Х                |

| set 1,1                | \$CB, \$CD          | 2F               | Х                | Х                |

| set 1,(hl)             | \$CB, \$CE          | 2F + 1R + 1W + 1 | 3F + 1R + 1W + 1 | 3F + 1R + 1W + 1 |

| set 1,(ix+n)           | \$DD, \$CB, \$CE, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| set 1,(iy+n)           | \$FD, \$CB, \$CE, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

| set 2,a                | \$CB, \$D7          | 2F               | Х                | Х                |

| set 2,b                | \$CB, \$D0          | 2F               | Х                | Х                |

| set 2,c                | \$CB, \$D1          | 2F               | Х                | Х                |

| set 2,d                | \$CB, \$D2          | 2F               | Х                | Х                |

| set 2,e                | \$CB, \$D3          | 2F               | Х                | Х                |

| set 2,h                | \$CB, \$D4          | 2F               | Х                | Х                |

| set 2,1                | \$CB, \$D5          | 2F               | Х                | Х                |

| set 2,(hl)             | \$CB, \$D6          | 2F + 1R + 1W + 1 | 3F + 1R + 1W + 1 | 3F + 1R + 1W + 1 |

| set 2,(ix+n)           | \$DD, \$CB, \$D6, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |

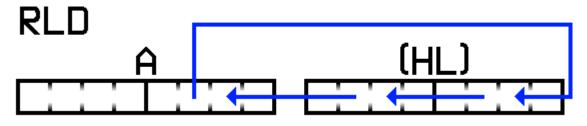

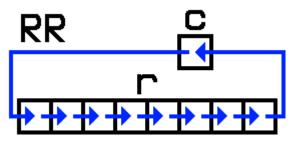

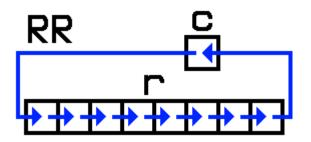

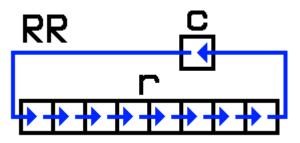

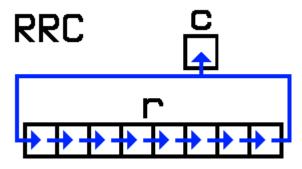

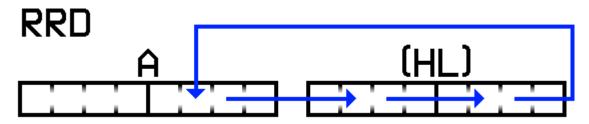

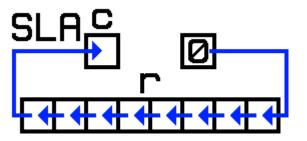

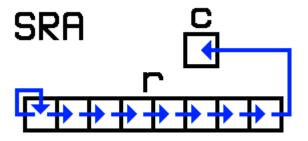

| set 2,(iy+n)           | \$FD, \$CB, \$D6, n | 4F + 1R + 1W + 1 | 5F + 1R + 1W + 1 | 5F + 1R + 1W + 1 |